Abstract

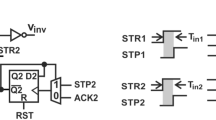

This paper investigates a number of design techniques to improve the linearity of gated Vernier delay line time integrators and their applications in \(\Delta \Sigma\) time-to-digital converters. Current-starved inverter delay stages whose charging and discharging currents are less dependent on the output voltage of the delay stages are used to improve the linearity of time-to-voltage conversion. A current-steering scheme is proposed to accommodate smoothing toggling between right-shift and left-shift operations so as to minimize skew errors. Isolation buffers are inserted between the delay lines and catch-detect DFFs to minimize the impact of the uneven input capacitance of the clock and data ports of the catch-detect DFFs. Metastability reduction techniques for TSPC DFFs are utilized to minimize metastability-induced errors in catch detection. In addition, the per-stage-delay of the slow and fast lines are made larger as compared with the delay of catch-detect DFFs to ensure the arrival of catch-detect flags at the next stage prior to the arrival of the signal to eliminate run-away errors. The proposed time integrator is utilized in a first-order single-bit \(\Delta \Sigma\) TDC to demonstrate its effectiveness. Designed in a TSMC 130 nm 1.2 V CMOS technology and analyzed using Spectre with BSIM3 device models, the pre-layout simulation results of the time integrator show that the time integrator exhibits a 20 dB improvement in spurious-free dynamic range as compared with time integrators with gated static inverter delay stages.

Similar content being viewed by others

Data availability

The authors declare that all data supporting the findings of this study are available within the article.

References

Lee, S., Kim, B., & Lee, K. (1997). A novel high-speed ring oscillator for multiphase clock generation using negative skewed delay scheme. IEEE J. Solid-State Circuits, 32(2), 289–291.

Yuan, F., & Parekh, P. (2020). Time-based all-digital \(\Delta \Sigma\) time-to-digital converter with pre-skewed bi-directional gated delay line time integrator. IET Circuits, Devices and Systems, 14(1), 25–34.

Lee, D., Yuan, F., Khan, G., & Zhou, Y. (2021). A 8-bit digital-to-time converter with pre-skewing and time interpolation. IET Circuits, Devices and Systems, 15(7), 670–685.

Jansson, J., & Kostamovaara, J. (2009). Synchronization in a multilevel CMOS time-to-digital converter. IEEE Transactions on Circuits and Systems I: Regular Papers, 56(8), 1622–1634.

Lu, P., Wu, Y., & Andreani, P. (2012) A 90 nm CMOS digital PLL based on vernier-gated-ring-oscillator time-to-digital converter. In Proceedings of the IEEE international symposium on circuits and systems (pp. 2593–2596).

Ali-Bakhshian, M., & Roberts, G. (2012). A digital implementation of a dual-path time-to-time integrator. IEEE Transactions on Circuits and Systems I: Regular Papers, 59(11), 2578–2591.

Hong, J., Kim, S., Liu, J., Xing, N., Jang, T., Park, J., Kim, J., Kim, T., & Park, H. (2012). A 0.004 mm\(^2\) 250 \(\mu\)W \(\Delta \Sigma\) TDC with time-difference accumulator and a 0.012 mm\(^2\) 2.5 mW bang-bang digital PLL using PRNG for low-power SoC applications. In IEEE international solid-state circuits conference digest of technical papers (pp. 240–242).

Yuan, F., & Parekh, P. (2020). Analysis and design of an all-digital \(\Delta \Sigma\) TDC via time-mode signal processing. IEEE Transactions on Circuits and Systems II, 67(6), 994–998.

Parekh, P., Yuan, F., & Zhou, Y. (2021). Gated vernier delay line time integrator with applications in delta-sigma time-to-digital converter. Microelectronics Journal.

Kim, K., Yu, W., & Cho, S. (2014). A 9 bit, 1.12 ps resolution 2.5 b/stage pipelined time-to-digital converter in 65nm CMOS using time-register. IEEE Journal of Solid-State Circuits, 49(4), 1007–1016.

Mantyniemi, A., Rahkonen, T., & Kostamovaara, J. (2009). A CMOS time-to-digital converter (TDC) based on a cyclic time domain successive approximation interpolation method. IEEE Journal of Solid-State Circuits, 44(11), 3067–3078.

Chung, H., Ishikuro, H., & Kuroda, T. (2012). A 10-bit 80-MS/s decision-select successive approximation TDC in 65-nm CMOS. IEEE Journal of Solid-State Circuits, 47(5), 1232–1241.

Parekh, P., Yuan, F., & Zhou, Y. (2021). Improved metastability of true single-phase clock d-flipflops with applications in vernier time-to-digital converters. IEEE Transactions on Circuits and Systems I.

Parekh, P., Yuan, F., & Zhou, Y. (2020) All-digital time integrator using bi-directional gated vernier delay line. In Proceedings of the IEEE international Midwest symposium on circuits and systems (pp. 321–324).

Lin, J., & Hsieh, C. (2015). A 0.3 V 10-bit 1.17 f SAR ADC with merge and split switching in 90 nm CMOS. IEEE Transactions on Circuits and Systems I: Regular Papers, 62(1), 70–79.

Yuan, F. (2021). Bootstrapping techniques for energy-efficient SAR ADCs: A state-of-the-art review. In Proceedings of Midwest symposium on circuits and systems (pp. 1–4).

Yuan, F. (2018). Design techniques of all-digital arithmetic units for time-mode signal processing. IET Circuits, Devices and Systems, 12(6), 753–763.

Park, K., & Park, J. (1999). Time-to-digital converter of very high pulse stretching ratio for digital storage oscilloscope. Review of Scientific Instruments, 70(2), 1568–574.

Lee, M., & Abidi, A. (2008). A 9B, 1.25 ps resolution coarse-fine time-to-digital converter in 90 nm CMOS that amplifies a time residue. IEEE Journal of Solid-State Circuits, 43(4), 769–777.

Kim, K., Kim, Y., Yu, W., & Cho, S. (2013). A 7b 3.75 ps resolution two-step time-to-digital converter in 65 nm CMOS using pulse-train time amplifier. IEEE Journal of Solid-State Circuits, 48(4), 1009–1017.

Park, Y., Amor, D., & Yuan, F. (2016) Time integrator for mixed-mode signal processing. In Proceedings of the IEEE international symposium on circuits and systems (pp. 826–829).

Parekh, P., Yuan, F., & Zhou, Y. (2021) Gated vernier delay line time integrator for time-mode signal processing. In Proceedings of the IEEE Midwest symposium on circuits and systems (pp. 1082–1085).

Zhu, K., Feng, J., Lyu, Y., & He, A. (2018). High-precision differential time integrator based on time adder. Electronics Letters, 54(22), 1268–1270.

Ji, X., Wang, Y., Shen, M., & Guo, Y. (2020). Error-compensated time integrator in 28-nm CMOS technology. Electronics Letters, 56(16), 806–807.

Karmakart, A., Smedt, V. D., & Leroux, P. (2021). Pseudo-differential time-domain integrator using charge-based time-domain circuits. In Proceedings of the IEEE Latin American symposium on circuits and systems (pp. 1–4).

Park, Y., & Yuan, F. (2017). All-digital delta-sigma TDC with differential bi-directional gated-delay-line time integrator. In IEEE Midwest symposium on circuits and systems (pp. 1513–1516).

Taillefer, C., & Roberts, G. (2009). Delta-sigma A/D converter via time-mode signal processing. IEEE Transactions on Circuits and Systems I, 56(9), 1908–1920.

Firdauzi, A., Xu, Z., Miyahara, M., & Matsuzawa, A. (2016). A 74.9 dB SNDR 1 MHz bandwidth 0.9 mW delta-sigma time-to-digital converter using charge pump and SAR ADC. In Proceedings of the IEEE international symposium on circuits and systems (pp. 57–60).

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Parekh, P., Yuan, F. & Zhou, Y. \(\Delta \Sigma\) Time-to-digital converter with current-steering vernier time integrator. Analog Integr Circ Sig Process 114, 325–343 (2023). https://doi.org/10.1007/s10470-022-02116-w

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-022-02116-w