Abstract

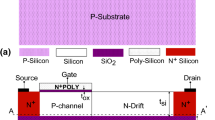

To increase the breakdown voltage and reduce the on-state resistance, a novel Lateral Double Diffused Metal Oxide Semiconductor (LDMOS) field-effect transistor is proposed in this paper. In the proposed structure, double P-trenches are inserted in the buried oxide under the source and drain regions. The proposed device is called as the double p-trench deep gate LDMOS (DPTDG-LDMOS). By optimizing the P-trenches, the electric field will be more uniform, and so the maximum breakdown voltage obtains. Our simulation results show that the breakdown voltage, on-state resistance, maximum temperature (TMAX), and figure of merit (FOM) for the DPTDG-LDMOS are improved in comparison with a conventional LDMOS.

Similar content being viewed by others

Data Availability

The data that support the findings of this study are openly available at http:// www.silvaco.com, reference number [19].

References

Matsumoto S, Kim I, Sakai T, Fukumitsu T, Yachi T (1995) Switching characteristics of a thin film SOI power MOSFET. Jpn J Appl Phys 34:817–821

Erlbacher T (2014) Lateral power transistors in integrated circuits. Springer

Shenai K (1992) Optimized trench Mosfet technologies for power devices. IEEE Trans. Electron Devices 39:1435–1443

Hong JH, Chung SK, Choi YI (2004) Optimum design for minimum on-resistance of low voltage trench power MOSFET. Microelectron J 35:287–289

A. Narazaki, J. Maruyama, T. Kayumi, H. Hamachi, J. Moritani, S. Hine (2000) A 0.35 mm trench gate MOSFET with an ultra on state resistance and a high destruction immunity during the inductive switching. Proce. ISPSD, Toulouse, Fr. 377–380

Appels JA, Vaes HMJ (1979) High voltage thin layer devices (Resurf devices). Adv Chem Ser:238–242

Hardikar S, Tadikonda R, Green DW, Vershinin KV, Narayanan EMS (2004) Realizing high-voltage junction isolated LDMOS transistors with variation in lateral doping. IEEE Trans. Electron Devices 51:2223–2228

Singh Y, Rawat RS (2015) High figure-of-merit SOI power LDMOS for power integrated circuits. Eng Sci Technol an Int J 18:141–149

Hanaei M, Orouji AA, Ramezani Z, Amiri IS (2020) A silicon on nothing LDMOS with two air pillars in gate insulator for power applications. Silicon 12:2581–2586

T.R. Efland, C.Y. Tsai, S. Pendharkar (1998) Lateral thinking about power devices (LDMOS). Tech. Dig. - Int. Electron Devices Meet. 679–681

M. Zitouni, F. Morancho, P. Rossel, H. Tranduc, J. Buxo, and I. Pages, (1999) New concept for the lateral DMOS transistor for smart power IC’s. IEEE Int. Symp. Power Semicond. Devices ICs 73–76

Anvarifard MK (2017) An impressive structure containing triple trenches for RF power performance (TT-SOI-MESFET). J Comput Electron 17:230–237

Xu S, Gan KP, Samudra GS, Liang YC, Sin JKO (2000) 120 V interdigitated-drain LDMOS (IDLDMOS) on SOI substrate breaking power LDMOS limit. IEEE Trans Electron Devices 47:1980–1985

Anvarifard MK (2016) Superlattices and microstructures symmetrical SOI MESFET with a dual cavity region (DCR-SOI MESFET) to promote high-voltage and radio-frequency performances. Superlattice Microst 98:492–503

Anvarifard MK (2017) Creation of a new high voltage device with capable of enhancing driving current and breakdown voltage. Mater Sci Semicond Process 60:60–65

Orouji AA, Moghadam HA, Dideban A (2010) Double window partial SOI-LDMOSFET: a novel device for breakdown voltage improvement. Phys E Low-Dimensional Syst Nanostructures 43:498–502

Orouji AA, Sharbati S, Fathipour M (2009) A new partial-SOI LDMOSFET with modified electric field for breakdown voltage improvement. IEEE Trans Device Mater Reliab 9:449–453

Mehrad M, Orouji AA (2012) New trench gate power MOSFET with high breakdown voltage and reduced on-resistance using a SiGe zone in drift region. Curr Appl Phys 12:1340–1344

Device Simulator ATLAS, Silvaco, International, 2012

Luo X, Zhang B, Li Z (2008) New high-voltage (> 1200 V) MOSFET with the charge trenches on partial SOI. IEEE Trans Electron Devices 55:1756–1761

Cheng X, Song Z, Dong Y, Yu Y, Shen D (2005) Patterned silicon-on-insulator technology for RF power LDMOSFET. Microelectron Eng 81:150–155

M. Inada, S. Yagi, Y. Yamamoto, G. Piao, M. Shimizu, H. Okumura and K. Arai, in: Proceedings of the IEEE International Symposium on Power Semiconductor Devices and IC's (ISPSD), (2006) 1–4

Orouji AA, Pak A (2015) A novel technique for electric field control to improve breakdown voltage. Mater Sci Semicond Process 34:230–235

Amin. Pak, Ali A. Orouji, A novel technique at LDMOSs to improve the figure of merit, 2Superlattices Microstruc 93 (2016) 11–17

Singh Y, Punetha M (2013) A lateral trench dual gate power MOSFET on thin SOI for improved performance. ECS J Solid State Sci Technol 2:113–117

Author information

Authors and Affiliations

Contributions

Conceptualization, Methodology, Formal analysis and investigation, and Writing - original draft preparation: [Amir Gavoshani].

Writing - review and editing, Funding acquisition, Resources, and Supervision: [Ali A. Orouji].

Writing - review and editing, Resources: [Abdollah Abbasi]

Corresponding author

Ethics declarations

Conflict of Interest

The Authors declare that there is no conflict of interest.

Ethical Approval

This article does not contain any studies with human participants or animals performed by any of the authors.

Informed Consent

Informed consent was obtained from all individual participants involved in the study.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Gavoshani, A., Orouji, A.A. & Abbasi, A. A Novel Deep Gate LDMOS Structure Using Double P-Trench to Improve the Breakdown Voltage and the On-State Resistance. Silicon 14, 597–602 (2022). https://doi.org/10.1007/s12633-020-00857-9

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-020-00857-9