Abstract

Multiple-valued logic such as ternary logic has attracted the digital system designers attention in recent years as it offers the benefits of reduced interconnects, higher operating speeds and smaller chip area. A goal of multi-threshold circuit design could be easily achieved by incorporating the scalable threshold voltage values of carbon nanotube field effect transistors (CNTFETs). This paper proposes a novel design of low-power and high-performance ternary adder and subtractor circuit design by combining the futuristic ternary and conventional binary logic design approaches. The simplified design of ternary to a binary decoder based on negative ternary inverter and positive ternary inverter outputs, and further transmission gate-based ternary multiplexer implementation facilitates the low power consumption and energy efficiency in the implementation of the complex arithmetic circuits. Extensive HSPICE simulations are conducted with the standard 32 nm CNTFET technology in order to evaluate the performance metrics of the realized circuits. According to the simulation results, proposed ternary adder and subtractor cells show the significant improvement in energy consumption (PDP) as compared to their counterparts under different test conditions. Moreover, the ripple adder structure is realized using the proposed adder circuit in order to test the practicability of given circuits in cascaded structures.

Similar content being viewed by others

1 Introduction

With the emergence of portable electronic devices such as media and image processors, energy conservation is the primary requirement of the VLSI industry. Feature size scaling is the prominent method in order to cope up with Moore’s law, exponential growth. But, scaling down the feature size of current CMOS technology further into nano-range causes several critical challenges such as decreased gate controllability, increase in the sub-threshold current due to punch through, short channel effects, large process variations and so on [23]. Therefore MOS-based devices are no more found to be a suitable candidate for the realization of energy-efficient systems. Hence, researchers are taking into consideration the emerging technologies such as carbon nanotube field effect transistor (CNTFET) [24], quantum dot cellular automata (QCA), single electron transistors (SET), fin-shaped field effect transistors (FINFETs), etc.

Among various devices, CNTFET is the most suitable alternative to replace existing silicon devices due to its advantageous electrical characteristics such as low power consumption due to reduced leakage component, excellent carrier mobility and high current carrying capability [12, 24]. CNTFETs’ other exceptional features include one-dimensional band structure which suppresses back-scattering, near ballistic operation [12], geometry-dependent threshold voltage, and same mobility of P- and N-type CNTFETs further favors the transistor sizing of complex circuits [5, 13, 21]. Another unique property of CNTFET is that it provides the flexibility to control the threshold voltage by adopting the CNT diameters of different values [21]. This feature makes them a more viable option to design various voltage mode multi-valued logic (MVL) circuits [14].

The main predicament observed when a binary logic is employed to implement the complex VLSI systems is that approximately 70% of the area is occupied by on-chip and off-chip interconnections while only 10% is occupied by the active devices [4]. In order to cope up with the increasing interconnections with the rise in chip density, MVL provides an alternative solution [21]. MVL offers manifold advantages over classical binary logic. Firstly, overall chip area is diminished as more amount of information is transmitted over the same wires. Secondly, the complexity of the circuit is reduced since each MVL element is capable of processing more information. Further serial and serial, parallel arithmetic operations are carried out faster as transmitted data per unit time is increased [28]. Among various MVL systems, ternary logic with radix 3 is more efficient, as natural numbers are the preferable radixes for the complex computation. Since arithmetic function implementation using three-valued logic, requiring a lesser number of operations, results in fewer gates and signal lines, ternary logic helps to achieve a significant power and area efficiency in digital system design as compared to classical binary logic [1]. For example, 14-bit binary addition could be done using 9-bit ternary adder.

However, in MVL system, the most critical issue which needs to be dealt with is the cross talk effects in interconnects carrying MVL signals. The cross talk effects in ternary logic are investigated [21] using the multi-wall carbon nanotube (MWCNT) bundles and have been compared with the copper interconnects. For the ternary logic, the power consumption, energy consumption and worst-case cross talk delay of MWCNT interconnects are significantly lower than those of copper wires. Moreover, as compared to copper wires, interconnects using MWCNT have lower cross talk noise voltage as well as the area in ternary logic. However, worst-case cross talk noise glitch amplitude crosses the switching threshold of receivers in both types of compared interconnects [21]. Therefore cross talk elimination is an important issue in the designing of CNT ternary systems. MVL implementation is feasible with the multi-threshold design which in turn can be easily accomplished by employing the CNTs with different chirality vector as compared to single threshold MOS devices [14].

Since addition is the primary operation employed in various arithmetic unit-based computational systems such as microprocessors, DSP processor, and other multimedia-based architectures. In order to perform other arithmetic operations such as subtraction and multiplication in complex circuits, the full adder cell is duplicated several times. Thus improving the performance of the core module of the circuit will result in the overall improvement in performance of the whole arithmetic system. Several ternary logic-based adder circuits are available in the literature [2, 8,9,10, 16,17,18, 22, 25,26,27].

This article presents the new designs of combinational circuits such as a ternary half adder, full adder, ripple carry adder, and subtractor circuit based on the new multiplexer design. Also, the multiplexer is based on simplified negative ternary inverter and positive ternary inverter-based decoder circuit. Further the adder and subtractor circuits are implemented based on the combination of ternary to binary decoder and new multiplexer design [14]. The proposed designs combine the advantages of ternary logic and binary logic. Since binary logic is efficient in performing fast computation and the ternary logic is a good candidate for decoding block, the resultant proposed circuits are based on the combination of both the logic. The new transmission gate-based multiplexer circuit is designed using the simplified decoder design [22]. Further, these new multiplexer circuits are used to realize the ternary adder and subtractor circuits.

The paper is organized as follows: In Sect. 2, a brief review of CNTFET device is done. The new low power ternary full adder and subtractor circuits are proposed in Sect. 3. Investigation of experimental results and comparison are shown in Sect. 4. Finally, the conclusion is made in Sect. 5.

2 Overview of CNTFET

A CNT structure is made by rolling one or more graphite sheet layers along a wrapping vector. If it is constructed using a single layer of the graphite sheet, it is known as single wall CNT (SWCNT), while if it is composed of multiple graphite sheet layers then it is termed as multi-wall CNT (MWCNT) [15]. The arrangement of the carbon atoms along the tube defines the chirality vector, and it is specified by an integer pair (n1, n2). Based on a chiral vector, CNT can be conducting or semiconducting. If the nanotube is metallic, then \(n1=n2\) or \(n1-n2=3i\), where i is an integer otherwise it is semiconductor [24]. CNT diameter plays a key role in deciding the device electrical properties such as its modes of operation, transitional frequency, molecular size, and threshold voltage [6].

The diameter of the CNT is calculated from the following equation:

where \({a}_{0}=0.142\) nm, \(\pi =3.14\) and integer pairs (n1, n2) indicates the chirality vector. In the construction of CNTFET devices, one or array of undoped semiconducting SWCNTs are employed as a conducting channel material instead of bulk silicon used in the MOS structure. As a result, movement of the electron is confined only in 1-dimensional space which leads to an increment in carrier mobility on account of ballistic transport operation [19]. The decrement in the power dissipation through the CNTFET device is observed due to the ballistic conduction in CNT. Also, the device operational speed rises as CNTs are having a high density of ON current and higher \(I_\mathrm{on}\)/\(I_\mathrm{off}\) ratio as compared to their silicon counterparts. Also, same current driving capability of P/N-type CNTFET further simplifies the transistor sizing of complex CNTFET-based circuits. These unique characteristics of CNTFET device make them a suitable alternative to MOSFET for high-performance applications. The CNTFET approximate calculation of gate width is given by the following equation [3]:

where \(W_\mathrm{min}\), N and S indicate the minimum gate width, number of tubes and pitch, respectively. Pitch is the distance between two adjoining CNTs under the same gate.

The principle of operation and the I–V characteristics of the CNTFET devices are similar to classical silicon-based devices. Analogous to the MOSFETs, gate threshold voltage is required in order to establish an electrostatic channel between two highly doped source and drain regions. The threshold voltage of the CNTFET is computed using (2) [3].

As seen from the above equation, there is an inverse relationship existing between the threshold voltage and the CNT diameter. For instance, CNTFET with a chirality vector of (19,0) has a CNT diameter of 1.487 nm and a corresponding threshold voltage is 0.293 V. Hence the alteration in threshold voltage could be easily achieved just by adjusting the CNT diameter values [21]. This unique characteristic of CNTFET makes them suitable to be employed in multi-threshold circuits in digital system design.

CNTFETs are classified into three categories, namely Schottky barrier CNTFET (SB-CNTFET), band to band CNTFET (T-CNTFET) and MOSFET like CNTFET. SB-CNTFET are based on the direct tunneling through the way of Schottky barrier between the metal and the nanotube. The predicament of this type of CNTFETs is that they have reduced current delivering capability which in turn hampers the speed of the device. Hence it limits its usage in CMOS logic families implementation. A band to band tunneling CNTFET has low on current, considerable cutoff characteristics, and is apt for sub-threshold applications [20]. In an attempt to achieve field effect behavior and unipolar characteristics, undoped CNT channel is embedded between two highly doped regions resulting in a MOSFET-like CNTFET. This CNTFETs have similar mechanical and electrical characteristic as that of earlier versions of MOSFETs. Hence, in this article MOSFET like CNTFET is used in order to realize the proposed circuits.

3 Proposed Circuits

In this section, ternary arithmetic circuits are proposed based on the combination of ternary logic and the binary logic. Initially, a ternary multiplexer circuit is proposed using the CNTFET-based transmission gates. Then ternary half adder, full adder, subtractor, and ripple carry adder circuits are designed using proposed multiplexer circuit.

The existing adder designs in the literature are in general categorized into two wider approaches. In the first approach, ternary to binary conversion is done using a decoder circuit. Then all the processing on the operands is performed on binary values. Later these intermediate binary values are fed to the encoder circuits to obtain the ternary outputs. The ternary half adder based on this strategy is explained in [14, 22]. The ternary adder and subtractor based on the above method are described in [25]. Almost all such types of adder circuits are realized using CMOS logic design style.

In the second method, no encoder and decoder circuits are employed rather directly the computations are performed on the ternary values. Hence the designs using this approach are explained in [2, 9, 10, 26, 27]. Among various designs, [2, 26, 27] presents the adder design implementation by using ternary multiplexer circuits with predecessor and successor as the input data. In all the existing multiplexer-based designs, the input data to the multiplexer are ternary values. The circuits [9, 10] use various versions of the inverter as the input to realize each of the input combinations individually. The technique employed to realize the proposed circuits is based on a combination of both the approaches. The decoder and encoder are used to perform ternary to binary conversion and vice versa. The circuit implementation is done using the proposed ternary multiplexer rather than CMOS implementation.

3.1 Proposed Ternary Multiplexer

Ternary logic is a subset of MVL consists of 3 logic levels low, mid, and high corresponding to 0, \({V_\mathrm{dd}/2}\), and \({V_\mathrm{dd}}\) voltage values. The proposed ternary multiplexer is designed using the one input and two output ternary decoder circuit and a two input binary NAND circuit. For ternary input signal A, the decoder outputs are NTI(A) and PTI(A) for which the truth table is shown in Table 1. In the proposed design, the decoder function, i.e., ternary to binary conversion, is performed by using a negative ternary inverter (NTI) and positive ternary inverter (PTI) [14]. It should be noted that ternary to binary conversion before performing the actual computation is much simplified and efficient in our design as compared to previous decoder circuits. For example, decoder [14] is realized using two NTI, one PTI, and one standard ternary NOR (STNOR).

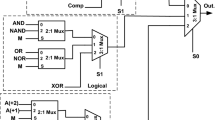

Figure 1 shows the schematic design of the proposed ternary multiplexer. For the given figure, the numbers show the chiral vector taken for the respective CNTs. The truth table of the proposed multiplexer is indicated in Table 2, where S is the select signal and \({D}_{0}\), \({D}_{1}\), and \({D}_{2}\) are the input data lines. The control signals which are fed to the gate of P-type and N-type transistors are indicated in Table 2. The control signals required are NTI(S), S1, and PTI(S), respectively. The NTI(S) and PTI(S) are generated using the inverter circuits of [14]. And the S1 signal is created by performing a NAND operation between PTI(S) and \(\overline{{\hbox {NTI}}(S)}\) as shown in multiplexer figure. The operation of the multiplexer is described as follows: when select signal \(S=0\), the input corresponding to \({D}_{0}\) is passed to the output. The control signals in this case are S and the NTI(S). When the value of \(S=1\) occurs, control signals \(\overline{S1}\) and S1 are used and the input \({D}_{1}\) is transmitted to the output. And when \(S=2\) condition occur, control signals PTI(S) and S are fed to select the \({D}_{2}\) at the output.

The comparison of the proposed multiplexer is mentioned in Table 2. It demonstrates that in all three of the multiplexer circuits the control signals used to select the input data \(D_0\) are S and NTI(S), while the control signals used to select input data \(D_2\) are PTI(S) and S, respectively. The main difference that arises is in the realization of the selection of data corresponds to \(D_1\). The multiplexer design [26] exploits predecessor and \(\overline{{\hbox {predecessor}}}\) unary cycle operators, as the control signals in order to select the data corresponds to \(D_1\). Further the predecessor circuit [26] is having high power consumption due to availability of a direct path between supply and ground. Therefore, in spite of less device count of the whole structure, the power consumption of the final multiplexer circuit is high. In order to select the \(D_1\) input in the multiplexer circuit [27], S, NTI(S), and PTI(S) are fed to four different transistors. On the other hand, in the proposed multiplexer circuit, NAND of PTI(S) and \(\overline{{\hbox {NTI}}(S)}\) are used as the control signal to fetch the \(D_1\) input data.

The proposed methodology to design ternary full adder and subtractor circuits is based on the proposed CNTFET-based transmission gate multiplexer circuit.

3.2 Proposed Ternary Half Adder

Ternary half adder (THA) consists of two inputs A and B and two outputs, Sum and Carry (Cy). Figure 2 shows the proposed design for ternary half adder circuit.

The functionality of proposed THA is given in Table 3. Initially ternary to binary conversion is done after taking NTI and PTI of an input [14]. The analysis of Table 3 reveals that when the summation of two inputs is 1, intermediate signal \(H-S1\) is at high logic. Similarly, when the summation of two inputs is 2, intermediate signal \(H-S2\) is at high logic. Hence all the input combinations which are generating sum output as logic 1 are stored in \(H-S1\) while all the input transitions, producing sum output as logic 2, are stored in another variable \(H-S2\). These two intermediate signals \(H-S1\) and \(H-S2\) are realized using two multiplexers (Fig. 2) with control signal as B. The three inputs applied to the multiplexer are \(\overline{A1}\), \(\overline{{\hbox {NTI}}(A)}\) and PTI(A), respectively. Analogous to multiplexer select signal, \(\overline{A1}\) is obtained as NAND of PTI(A) and \(\overline{{\hbox {NTI}}(A)}\). The intermediate outputs (\(H-S1\) and \(H-S2\)) are then fed to two input encoder circuit (Enc.1) to get the final ternary Sum output. Similarly, intermediate carry signal \(H-Cm\) is generated corresponding to the input combinations where carry output is present. The \(H-Cm\) is realized using one multiplexer with B as the control signal and \(V_\mathrm{dd}\), PTI(A), and NTI(A) as the multiplexer inputs. The multiplexer is followed by one input encoder (Enc.2) to obtain a final ternary output.

The proposed THA is different from other prevailing multiplexer-based designs. For instance, the design [26] is realized using ternary multiplexer but the input trits to the multiplexer are the successor and predecessor operators. Similarly, in THA [2] design, the input trits fed to the transmission gates are cycle operators. The transmission gate control signal is generated through the decoder signals [14]. While the input data fed to the proposed multiplexer-based THA is obtained from NTI, PTI, and NAND of an input. The one input two output decoder is employed in THA [22], but in the proposed adder simplified NTI and PTI circuits perform the decoder function. Also, the THA [22] circuit implementation is based on classical CMOS logic while proposed THA is based on the multiplexer. As the number of intermediate signals generated is only two for sum output, the equivalence of literals cannot be observed in the half adder design.

As seen from the Fig. 2 of half adder circuit, two encoder circuits are used in sum and carry generator circuits. To convert sum binary outputs (\(H-S1\) and \(H-S2\)) into ternary, encoder 1 or two input encoder (Fig. 3a) is used while encoder 2 or one input encoder (Fig. 3b) is utilized for binary to ternary conversion of intermediate carry signal (\(H-Cm\)). The number beside the transistors indicate the chirality vector taken for the respective CNTs.

In Encoder 1 circuit, switching action of different transistors depends on the inputs \(\overline{S1}\) and \(\overline{S2}\). When \(\overline{S1}\) input is low (0) and \(\overline{S2}\) is high (0.9), back to back connected transistor pair produce a high resistance path between supply and ground and generates the output logic 1. On the other hand when \(\overline{S2}\) input is low (0), logic 2 is directly transferred to the output through other path. For some cases when both \(\overline{S1}\) and \(\overline{S2}\) are high (0.9) two N-type transistors (with input \(\overline{S1}\) and \(\overline{S2}\)) pull the output toward logic 0. Similarly, in encoder 2 circuit, when the input \(\overline{Cm}\) is low (0), diode connected transistor perform voltage division and produces a logic 1 output. While if the \(\overline{Cm}\) is high (0.9), N-type transistor with input \(\overline{Cm}\) pulls the output to the ground.

3.3 Proposed Ternary Full Adder

Ternary full adder (TFA 2) consists of three ternary inputs A, B, and \(C_\mathrm{in}\) and two ternary outputs Sum and Carry (Cy). An extensive truth table for proposed full adder along with decoder signals (NTI A, PTI A) and intermediate Sum signals (\(F-S1\), \(F-S2\), \(F-S3\)) are indicated in Table 4. Analogous to THA intermediate outputs, \(F-S1\) and \(F-S2\) are the intermediate outputs, when \(C_\mathrm{in}=0\). Similarly \(F-S3\) and \(F-S4\) are the outputs when sum is at logic 1 and logic 2, respectively, corresponds to \(C_\mathrm{in}=1\) and \(F-S5\) and \(F-S6\) are the analogous outputs when \(C_\mathrm{in}=2\). It is to be noted here that \(F-S5\) and \(F-S6\) outputs are equivalent to \(F-S2\) and \(F-S3\) outputs respectively. Similarly, \(F-S4\) and \(F-S1\) column values are equivalent. Since intermediate outputs \(F-S4\), \(F-S5\), and \(F-S6\) are identical to other three remaining intermediate signals, they are not mentioned in Table 4.

Equivalence of intermediate signals

According to Table 4, when \(B=0\), \(B=1\) and \(B=2\), \(\overline{F-S1}\) is \(\overline{A1}\), \(\overline{{\hbox {NTI}}(A)}\) and \({\hbox {PTI}} A\) respectively. Similarly, when \(B=0\), \(B=1\) and \(B=2\), \(\overline{F-S2}\) is \({\hbox {PTI}} A\), \(\overline{A1}\), \(\overline{{\hbox {NTI}}(A)}\) respectively. And, when \(B=0\), \(B=1\) and \(B=2\), \(\overline{F-S3}\) is \(\overline{{\hbox {NTI}}(A)}\), \({\hbox {PTI}} A\), and \(\overline{A1}\) respectively. The transmission gate-based multiplexers are used to obtain three intermediate signals (\(F-S1\), \(F-S2\) and \(F-S3\)). The complete sum generator circuit is as shown in Fig. 4. The various permutations of the intermediate signals are given to the two input encoder circuit to obtain Sout0 (Sum when \(C_\mathrm{in}=0\) ), Sout1 (Sum when \(C_\mathrm{in}=1\)) and Sout2 (Sum when \(C_\mathrm{in}=2\)) shown in Fig. 4a–c, respectively. Finally, multiplexing with respect to third input, i.e., \(C_\mathrm{in}\) is done with another multiplexer shown in Fig. 4d to obtain the final Sum output.

The extended truth table of the carry generator circuit is presented in Table 5. From the Table 5, intermediate signal \(F-Cm0\) is high (0.9) for all the carry outputs when \(C_\mathrm{in}=0\) and \(F-Cm1\) denotes the carry outputs when \(C_\mathrm{in}=1\). When \(C_\mathrm{in}=2\), carry has three values 0, 1 and 2. Hence two intermediate signals are taken \(F-Cm2\) and \(F-Cm2'\). The \(F-Cm2\) stores all the carry outputs corresponding to logic 1, and \(F-Cm2'\) stores all the outputs correspond to logic 2. The carry generator of the proposed adder is demonstrated in Fig. 5. If B input is 0, 1 and 2, then \(\overline{F-Cm0}\) is \(V_\mathrm{dd}\), \({\hbox {NTI}} A\), \({\hbox {PTI}} A\) respectively is realized using multiplexer (Fig. 5a) and fed to one input encoder to obtain Cout0 (Carry output when \(C_\mathrm{in}=0\)). If \(B=0\), \(B=1\) and \(B=2\), \(\overline{F-Cm1}\) is \({\hbox {PTI}} A\), \({\hbox {NTI}} A\) and 0 respectively. The multiplexer output \(\overline{F-Cm1}\) is then given to one input encoder to get Cout1 (carry output when \(C_\mathrm{in}=1\)) output (Fig. 5b). In Fig. 5c, \(\overline{F-Cm2}\) and \(\overline{F-Cm2'}\) are generated and fed to two input encoder to obtain the output Cout 2 (carry output when \(C_\mathrm{in} =2\)). Another multiplexer, multiplex the earlier produced outputs (Cout0, Cout1 and Cout2) on third input \(C_\mathrm{in}\) and generates final Carry (Cy) output.

Adder designs [26, 27] also use the multiplexer circuit in order to implement the functionality. In those circuits, the input trits to the multiplexer are ternary values, namely predecessor and successor of the input operands. But as described clearly, proposed adder designs do not use the predecessor and successors signals to get the outputs.

It is worth to note here that the effect of equivalence property is not noticeable when the ternary half adder circuit is implemented using the proposed approach because in the case of half adder only two sum intermediate signals are generated. But the effect is more observable in complex circuits, namely ternary full adder and subtractor designs when the number of intermediate binary signals is more as compared to the former case. This equivalence property, due to the existence of symmetric intermediate binary values, after performing the ternary to binary conversion will result in the reduction in the transistor count of the overall final circuit. In the absence of this equivalence, three extra ternary multiplexers will be required to obtain first stage sum output. This, in turn, leads to further optimization in the energy consumption of the resultant circuit.

The applicability of proposed adder design in a larger circuit is tested by combining a THA and 3 T-FA1 to realize 4-trit ripple carry adder (Fig. 6). As seen from the Fig. 6 of ripple carry adder, the third output is fed from previous carry stage and the THA carry lies between 0 and 1. Hence reduced FA1 adder design is the circuit in which the third input carries two logic levels, i.e., 0 and 1. Hence this FA1 design is employed to realize the 4-stage ripple carry adder.

3.4 Proposed Ternary Subtractor

Ternary full subtractor is a combinational circuit, which is used to perform subtraction of three ternary numbers. It takes three inputs (B, A and C) and two outputs Difference (Diff.) and Borrow. The truth table of the ternary full subtractor for the difference output is shown in Table 6. The difference output when \(C=0\) has two intermediate outputs \(S-S1\) and \(S-S2\), respectively. \(S-S1\) is at high (0.9) logic when difference output is at logic 1, while \(S-S2\) is at high logic (0.9) when the difference output is at logic 2. Similarly, when \(C=1\), corresponding intermediate signals are \(S-S2\) and \(S-S3\) and when \(C=2\) they are \(S-S3\) and \(S-S1\). Again the equivalence among intermediate signals is observed as seen earlier in full adder design. Hence 3 intermediate signals are required instead of 6 to realize the final difference output.

These intermediate outputs are generated using the multiplexer circuit with B as the control input and \({\hbox {NTI}}(A)\), \({\hbox {PTI}} (A)\) and A1 as the data inputs in different combinations. Further, these intermediate signals are given to the two input encoder circuits to obtain the outputs Dout0, Dout1 and Dout2 as shown in Fig. 7a–c, respectively. Final multiplexing with respect to input C is performed in Fig. 7d to produce final difference output.

Table 7 represents the extended truth table for subtractor borrow output. The intermediate outputs \({\hbox {Bor}}-C0\) and \({\hbox {Bor}}-C1\) are at high logic (0.9) when borrow is present for \(C=0\) and \(C=1\), respectively. Since for \(C=2\), borrow takes 3 values 0, 1 and 2. Hence two intermediate outputs are taken \({\hbox {Bor}}-C2\) and \(\overline{{\hbox {Bor}}-C2'}\) correspond to output of logic 1 and logic 2, respectively.

The implementation of borrow generator circuit is demonstrated in Fig. 8. The intermediate output \({\hbox {Bor}}-C0\) is realized using a multiplexer with B as control input and inputs fed are \({\hbox {NTI}}(A)\), \({\hbox {PTI}}(A)\), and \(V_\mathrm{dd}\). When \(B=0\), \(B=1\) and \(B=2\), \({\hbox {Bor}}-C1\) is 0, \({\hbox {NTI}}(A)\) and \({\hbox {PTI}}(A)\) for the case of \(C=1\). Similarly, when \(C=2\) and B is varied from 0 to 2, \({\hbox {Bor}}-C2\) is \(\overline{{\hbox {NTI}}(A)}\), \(\overline{A1}\) and \({\hbox {PTI}}(A)\), respectively. These intermediate outputs are then fed to one or two input encoder circuits to obtain the outputs \({\hbox {Bo}}-{\hbox {out0}}\), \({\hbox {Bo}}-{\hbox {out1}}\) and \({\hbox {Bo}}-{\hbox {out2}}\) respectively (Fig. 8a–c). Further to get the final borrow output (Fig. 8d), multiplexing with respect to input C is done.

The method adopted to implement the subtractor circuit [25] is based on the negation of literals technique. Initially, one input three output decoder is used to convert ternary inputs to binary values. Then all the computations are done on binary values using binary AND and OR gates. In the last, ternary buffers are used to retrieve the ternary outputs. On the other hand, proposed subtractor circuit is constructed using multiplexers and encoder circuits as explained earlier. The circuit complexity is increased to a greater extent when it is employed to realize complex circuits [25]. The proposed circuit is optimized in terms of device count due to the existence of equivalent literals.

The proposed adder and subtractor designs have low power consumption in spite of decoder/encoder pair. The proposed design employs one decoder that is only for the one input while other inputs are used as such in ternary form. While earlier reported decoder/encoder designs such as [14, 22, 25] employs the same number of decoder as the number of inputs exists. For example, adder design [25] using three decoders correspond to three available inputs. Moreover, decoder [14] is mostly used to perform ternary to binary conversion which consists of 10 transistors. In proposed design, simple NTI and PTI of inputs are used as the decoder outputs which requires only four transistors. Also, all the earlier reported encoder/decoder-based designs are implemented using CMOS logic style which inherits the disadvantage of having a high input capacitance. In the proposed circuits, in order to minimize the hardware complexity of the final circuit, instead of CMOS implementation, multiplexer-based implementation is done and reduction in decoder signals has also been done. Moreover while constructing complex circuits such as full adder and subtractor, the presence of equivalent literals further reduces the overall complexity of the proposed circuits.

If an encoder/decoder-based designs are considered, then the ternary to binary signal transitions of all the available inputs is done while in our case ternary to binary conversion corresponding to only one input is done. Similarly, at the output side, the signal transitions corresponding to all the available input, intermediate signals have been undergone through the ternary buffer circuit to obtain the ternary outputs. In proposed case, only one input signal values are fed to encoder circuit. That is intermediate decoded outputs of remaining two inputs are absent in our case. Hence the number of signals that the circuit is handling has been reduced as compared to earlier existing designs [14, 25].

On the other hand, if multiplexer based designs are considered such as [2, 26, 27], their also intermediate signals such as predecessor, successor signals are produced and then they are fed to the multiplexer inputs. In adder design of [26], at first carry generator as a selection circuit is constructed using ternary multiplexer circuits taking first two inputs A and B. Later this selection circuit is used with third input to produce the final ternary outputs. Analogous in our proposed designs, signal undergoes a transition in two stages of multiplexing. Moreover, when complex circuits are constructed such as multi-trit adder, the utilization of reduced forms of adder such as FA1 is used to optimize the overall performance of the resultant circuit. Therefore the number of signal transitions and the intermediate inputs handled in the proposed designs are more or less the same as compared to other existing multiplexer based designs.

4 Comparative Evaluation

4.1 Environment Setup

This section presents the simulation results of proposed circuits and is compared with other latest designs reported in the literature [9, 10, 14, 16, 22, 25,26,27]. All the designs are simulated using synopsis HSPICE simulator with 32 nm Stanford CNTFET model [6, 7] at room temperature. This standard model is developed for enhancement mode unipolar MOSFET like CNTFETs, where each transistor posses one or more number of CNTs as its channel. It takes into account the various non-idealities such as schottky effects, the elastic scattering in the channel region, screening effect by the parallel CNTs for CNTFET and parasitic including source/drain and gate capacitances, and resistances. This model also incorporates a full trans capacitance network to render more exact dynamic and transient results. Table 8 illustrates the CNTFET model important parameters with their corresponding values and concise description. The number of tubes under the gate terminal for all the CNTs is taken as three. The transient response of the proposed ternary full adder circuit is shown in Fig. 9. Figure 10 shows the transient output of the ternary full subtractor circuit.

To estimate the performance comparison of proposed and existing ternary multiplexer circuits, simulation is conducted and results are shown in Table 9. The results reveal the improvement of power consumption and power-delay product in comparison with other designs. The proposed multiplexer has the minimum static power consumption in comparison with design [26, 27], respectively. The main predicament of the proposed multiplexer circuit is that it has more device count as compared to previously existing designs.

Table 10 compares the performance metrics such as average power consumption, maximum propagation delay and power-delay product (PDP) of proposed TFA and THA designs with other state-of-the-art designs [2, 9, 10, 16, 22, 25,26,27]. The simulation is performed at the operating frequency of 250 MHz and 500 MHz, 0.9 V supply voltage and 1 fF output load. TFA1 is the full adder in which third input lies in the range of 0 and 1, while in TFA2 all the three inputs are ternary inputs. The simulation results of TFA and THA design demonstrates the superiority of the proposed design in terms of power consumption and power-delay product (PDP) in contrast to earlier reported designs [2, 9, 10, 16, 22, 25,26,27]. The proposed TFA1 design offers the PDP improvement of about 34% with respect to TFA1 [27] at a 250 MHZ operating frequency, which is the best PDP after it. The high power consumption of predecessor and successor circuits which in turn are utilized to realize the THA and TFA circuits [26] results in highest PDP among all the compared circuits. According to the tabular results, the power consumption of the TFA2 is 1.42 times better than the design [25] at 250 MHz operating frequency. Table 7 results reveal that the static power consumption of proposed adder designs have been lower as compared to other designs.

Also, TFA design of [27] requires additional power supplies in order to implement intermediate \(\overline{{\hbox {predecessor}}}\) and \(\overline{{\hbox {successor}}}\) signals while the proposed design does not require any additional power supplies.

Table 11 illustrates the comparison of performance metrics of ternary full subtractor (TFS) and ternary half subtractor (THS) circuits at two different frequencies. As compared to the earlier reported design TFS [25], the percentage improvement in delay and PDP is 39% and 33%, respectively, with an increase in power of 8% only. While corresponding to a THS circuit, it is 49%, and 67% respectively.

To test the proposed adder circuits applicability to construct the large adders, 4-trit ternary ripple carry adder circuit is realized using the proposed THA and TFA circuits. The worst-case propagation delay is taken when the inputs are fed in such a way that it causes all the possible transitions at the output [16]. The simulation results for ripple carry adder circuits are reported in Table 12. According to the simulation results, the performance enhancement in power consumption and PDP is observed to be 87.10% and 87.31% in comparison with best reported work [16]. Hence it can be inferred from the simulation results of ripple adder circuits that the performance of the proposed circuit is satisfactory when employed in the cascaded adder structures.

Further, in order to examine the sensitivity of proposed circuit toward the temperature variation, simulations are conducted under different ambient temperatures ranging from 0 to 50 \(^{\circ }\)C at different supply voltages with operating frequency of 100 MHz and 1 ff output load. Figure 11 shows the variation of PDP with supply voltage and temperature TFA1 [27]. Power-delay product (PDP), supply voltage and temperature variation of proposed TFA1 design are indicated in Fig. 12.

The device count comparison among proposed and other existing half adder and full adder designs are presented in Fig. 13a, b, respectively. The figures indicate that the proposed design does not have the least device count but it lies in the middle of the highest and the lowest levels. The transistor count comparison of the subtractor circuit is included in Table 11. Intuitively proposed subtractor design requires a lesser number of transistors as compared to the design [25].

PDP of TFA1 versus supply voltage and temperature of TFA1 [27]

Figure 14 shows the four parameters defined to capture noise margin for the ternary logic gates [11]. The noise margin analysis is done using DC analysis in HSPICE. That is, during simulation one of the input is varied from 0 to \(V_\mathrm{dd}\) while the other two inputs are fixed to either of the values of 0, \(V_\mathrm{dd}/2\) or \(V_\mathrm{dd}\). The noise margin analysis of adder and subtractor circuits with regard to defined four parameters are plotted in Figs. 15 and 16, respectively. In the given figures, \({\hbox {NM}}_{0}\) and \({\hbox {NM}}_{2}\) are indicating for the extreme levels while \({\hbox {NM}}_{1-}\) and \({\hbox {NM}}_{1+}\) are showing for intermediate levels. The proposed designs show the best noise margin in comparison with other designs for the given output.

Another aspect of interest is the robustness of the proposed designs when subjected to CNT diameter and density variations. For this, Monte Carlo simulation is conducted using Gaussian distributions with 5, 10 and 15% variations at ± 3\(\sigma \) level. The energy variation of the proposed circuits with the CNT diameter and density variations is illustrated in Fig. 17a, b, respectively. It is clear from the figures that the proposed designs have less effect when prone to the variation in CNT diameter and density variations.

Hence the proposed designs exploit the combined merits of binary logic and ternary logic in order to obtain the significant improvement in performance parameters of the circuit.

5 Conclusion

In this article, we have presented the design of low power and energy-efficient ternary adder and subtractor circuits for nano-technology using futuristic CNTFET devices. The proposed circuit surpasses the other similar designs in terms of power consumption, mainly due to low power transmission gate style employed to realize the majority of the circuit. Moreover ternary to binary conversion is minimized to a greater extent to obtain further optimization of the performance metrics. Also, as the complexity of circuit rises, reduction in the area overhead is carried out because of the application of equivalence property due to symmetric values existing between various intermediate binary signals.

The multiplexing of output digits is performed using two-stage multiplexing using simplified decoder inputs bits of the ternary input values. Apparently proposed adder and subtractor designs show low power and enhanced performance as compared with earlier reported designs. Furthermore, simulation results confirm that proposed designs work well when prone to frequency, voltage, temperature and process variations. Hence it can be inferred that the proposed arithmetic circuit design by combining the ternary and binary logic provides a feasible solution to realize the efficient digital systems.

References

P.C. Balla, A. Antoniou, Low power dissipation MOS ternary logic family. IEEE J. Solid State Circuits 19(5), 739–749 (1984)

N.H. Bastani, M.H. Moaiyeri, K. Navi, Carbon nanotube field effect transistor switching logic for designing efficient ternary arithmetic circuits. J. Nanoelectron. Optoelectron. 12(2), 118–129 (2017)

K.Y. Bok, Y.B. Kim, F. Lombardi, Novel design methodology to optimize the speed and power of the CNTFET circuits, in Proceedings of the IEEE International Midwest Symposium on Circuits and Systems, Cancun, Mexico (2009), pp. 1130–1133

J.T. Butler, Multiple-Valued Logic in VLSI Design, IEEE Computer Society Press Technology Series. Los Alamitos, California

G. Cho, Y. Kim, F. Lombardi, M. Choi, Performance evaluation of CNFET-based logic gates, in Proceedings of the IEEE International Instrumentation and Measurement Technology Conference, Singapore (2009), pp. 909–991

J. Deng, H.S.P. Wong, A compact SPICE model for carbon-nanotube field-effect transistors including non idealities and its application—part I: model of the intrinsic channel region. IEEE Trans. Electron Device 54(12), 3186–3194 (2007)

J. Deng, H.S.P. Wong, A compact SPICE model for carbon-nanotube field-effect transistors including non-idealities and its application—part II: full device model and circuit performance benchmarking. IEEE Trans. Electron Device 54(12), 3195–3205 (2007)

A. Dhande, V. Ingole, Design and implementation of 2 bit ternary ALU slice, in Proceedings of the International Conference IEEE-Sciences of Electronic, Technologies of Information and Telecommunications (2005), pp. 17–21

S.A. Ebrahimi, P. Keshavarzian, S. Sorouri, Low power CNTFET-based ternary full adder cell for nanoelectronics. Int. J. Soft Comput. 2(2), 291–295 (2012)

F. Jafarzadehpour, P. Keshavarzian, Low-power consumption ternary full adder based on CNTFET. IET Circuits Devices Syst. 10(5), 365–374 (2016)

S. Karmakar, J. Chandy, F. Jain, Design of ternary logic combinational circuits based on quantum dot gate FETs. IEEE Trans. VLSI Syst. 21(5), 793–806 (2013)

Y.B. Kim, Challenges for nanoscale MOSFETs and emerging nano-electronics. Trans. Electr. Electron. Mater. 11(3), 93–105 (2010)

Y. Lin, J. Appenzeller, J. Knoch, P. Avouris, High-performance carbon nanotube field-effect transistor with tunable polarities. IEEE Trans. Nanotechnol. 4, 481–489 (2005)

S. Lin, Y.B. Kim, F. Lombardi, CNTFET-based design of ternary logic gates and arithmetic circuits. IEEE Trans. Nanotechnol. 10(2), 217–225 (2011)

P.L. McEuen, M. Fuhrer, H. Park, Single-walled carbon nanotube electronics. IEEE Trans. Nanotechnol. 1, 78–85 (2002)

R.F. Mirzaee, M.H. Moaiyeri, K. Navi, Dramatically low-transistor-count high-speed ternary adders, in 43rd International Symposium on Multiple-Valued Logic (2013), pp. 170–175

M.H. Moaiyeri, A. Doostaregan, K. Navi, Design of energy-efficient and robust ternary circuits for nanotechnology. IET Circuits Devices Syst. 5(4), 285–296 (2011)

M.H. Moaiyeri, R.F. Mirzaee, K. Navi, O. Hashemipour, Efficient CNTFET-based ternary full adder cells for nanoelectronics. Nano Micro Lett. 3(1), 43–50 (2011)

A. Rahman, J. Guo, S. Datta, M.S. Lundstrom, Theory of ballistic nanotransistors. IEEE Trans. Electron Devices 50, 1853–1864 (2003)

A. Raychowdhury, K. Roy, Carbon nanotube electronics: design of high-performance and low-power digital circuits. IEEE Trans. Circuits Syst. 54(11), 2391–2401 (2007)

M. Rezaeikhezeli, M.H. Moaiyeri, A. Jalali, Analysis of crosstalk effects for multiwalled carbon nanotube bundle interconnects in ternary logic and comparison with cu interconnects. IEEE Trans. Nanotechnol. 16(1), 107–117 (2017)

S.K. Sahoo, G. Akhilesh, R. Sahoo, M. Muglikar, High performance ternary adder using CNTFET. IEEE Trans. Nanotechnol. 16(3), 368–374 (2017)

S.K. Sinha, S. Chaudhury, Comparative study of leakage power in CNTFET over MOSFET device. J. Semicond. 35(11), 01–06 (2014)

S. Sinha, K.K. Kumar, S. Chaudhury, CNTFET: the emerging post-CMOS device, in International Conference on Signal Processing and Communication (ICSC) (2013), pp. 372–374

V. Sridevi, T. Jayanthy, Minimization of CNTFET ternary combinational circuits using negation of literals technique. Arab. J. Sci. Eng. 39(6), 4875–4890 (2014)

B. Srinivasu, K. Sridharan, Low-complexity multi-ternary digit multiplier design in CNTFET technology. IEEE Trans. Circuits Syst. 63(8), 753–757 (2016)

S. Tabrizchi, A. Panahi, F. Shari, K. Navi, N. Bagherzadeh, Method for designing ternary adder cells. IET Circuits Devices Syst. 11(5), 465–470 (2017)

X.W. Wu, F.P. Prosser, CMOS ternary logic circuits. Proc. IEEE Circuits Devices Syst. 137(1), 21–27 (1990)

Acknowledgements

This publication is an outcome of the R&D work undertaken project under the Visvesvaraya PhD Scheme of Ministry of Electronics and Information Technology, Government of India, being implemented by Digital India Corporation.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Sharma, T., Kumre, L. CNTFET-Based Design of Ternary Arithmetic Modules. Circuits Syst Signal Process 38, 4640–4666 (2019). https://doi.org/10.1007/s00034-019-01070-9

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-019-01070-9