Abstract

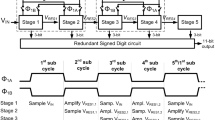

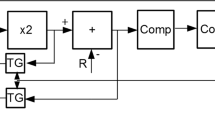

A new pipelined analog-to-digital converter (ADC) using second-generation current conveyor (CCII) is presented. Two main building blocks of the pipelined ADC, sample-and-hold (S/H) circuit and multiplying digital-to-analog converter (MDAC) are constructed of CCII instead of operational amplifier (OA). Experimental results show that the proposed CCII-based pipelined ADC can work at 12.5 MHz with a 7.3-bit resolution. The DNL is within −0.4 LSB and 0.4 LSB and INL is within −0.8 LSB and 0.8 LSB, respectively. The pipelined ADC is realized in TSMC 0.35 μm CMOS technology and consumes 29 mW under a 3.3 V power supply. The core size is 0.85×0.85 mm2.

Similar content being viewed by others

References

S.-Y. Chuang and T.L. Sculley, “A digitally self-calibrating 14-bit 10-MHz CMOS pipelined A/D converter,” IEEE Journal of Solid-State Circuits, vol. 37, no. 6, pp. 683–674, June 2002.

A.M. Abo and P.R. Gray, “A 1.5-V, 10-bit, 14.3-MS/s CMOS pipeline analog-to-digital converter,” IEEE Journal of Solid-State Circuits, vol. 34, no. 5, pp. 599–606, May 1999.

H.-S. Chen, B.-S. Song, and K. Bacrania, “A 14-b 20-MSamples/s CMOS pipelined ADC,” IEEE Journal of Solid-State Circuits, vol. 36, no. 6, pp. 997–1001, June 2001.

Y.-M. Lin, B. Kim, and P.R. Gray, “A 13-b 2.5-MHz self-calibrated pipelined A/D converter in 3-um CMOS,” IEEE Journal of Solid-State Circuits, vol. 26, no. 4, pp. 628–636, April 1991.

Y.-S. Hwang, L.-P. Liao, C.-C. Tsai, W.-T. Lee, and T.-Y. Lee, “A new CCII-based pipelined analog to digital converter,” in Proc. of IEEE International Symposium on Circuits and Systems (ISCAS), Kobe, Japan, May 2005, pp. 6170–6173.

Y.-S. Hwang, P.-T. Hung, W. Chen, and S.-I. Liu, “Systematic generation of current-mode linear transformation filters based on multiple output CCIIs,” Analog Integrated Circuits and Signal Processing, vol. 32, pp. 123–134, 2002.

D.-S. Wu, S.-I. Liu, Y.-S. Hwang, and Y.P. Wu, “Multiphe-phase sinusoidal oscillator using second-generation current conveyors,” International Journal of Electronics, vol. 78, no. 4, pp. 645–651, 1995.

A.A. Tutyshkin and A.S. Korotkov, “Current conveyor based switched-capacitor integrator with reduced parasitic sensitivity,” IEEE International Conference on Circuits and Systems for Communications, pp. 78–81, 2002.

J. Terada, Y. Matsuya, F. Morisawa, and Y. Kado, “8-mW, 1-V, 100-Msps, 6-bit A/D converter using a transconductance latched comparator,” IEEE Asia Pacific Conference on ASIC, pp. 53–56, Aug. 2000.

Acknowledgment

The authors would like to thank the National Science Council and Chip Implementation Center of Taiwan for the financial and technical supporting. The work was sponsored by NSC-94-2213-E-027-049.

Author information

Authors and Affiliations

Corresponding author

Additional information

Sing-Yen Wu received the M.S. degree in the Department of Electronic Engineering from National Taipei University of Technology, Taipei, Taiwan, in 2005. His current research interests include CMOS pipelined analog-to-digital converters and mixed-signal integrated circuit.

Lu-Po Liao received the M.S. degree in the Department of Electronic Engineering from National Taipei University of Technology, Taipei, Taiwan, in 2003. His current research interests include analog integrated circuit design and mixed-signal integrated circuit design.

Chia-Chun Tsai received the Ph.D. degrees in Electrical Engineering from National Taiwan University, Taipei, Taiwan, 1991. From 1989 to 2005, he served at the Department of Electronic Engineering, National Taipei University of Technology, Taipei, Taiwan. Since 2005 he has been with the Department of Computer Science and Information Engineering, Nanhua University, Chiayi, Taiwan, where he is a Full Professor. His current research interests include VLSI design automation and mixed-signal IC designs.

Rights and permissions

About this article

Cite this article

Hwang, YS., Chen, JJ., Wu, SY. et al. A new pipelined analog-to-digital converter using current conveyors. Analog Integr Circ Sig Process 50, 213–220 (2007). https://doi.org/10.1007/s10470-007-9031-2

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-007-9031-2