Abstract

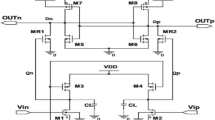

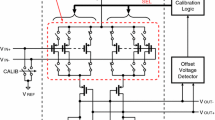

A novel dynamic latched comparator with offset voltage compensation is presented. The proposed comparator uses one phase clock signal for its operation and can drive a larger capacitive load with complementary version of the regenerative output latch stage. As it provides a larger voltage gain up to 22 V/V to the regenerative latch, the input-referred offset voltage of the latch is reduced and metastability is improved. The proposed comparator is designed using 90 nm PTM technology and 1 V power supply voltage. It demonstrates up to 24.6% less offset voltage and 30.0% less sensitivity of delay to decreasing input voltage difference (17 ps/decade) than the conventional double-tail latched comparator at approximately the same area and power consumption. In addition, with a digitally controlled capacitive offset calibration technique, the offset voltage of the proposed comparator is further reduced from 6.03 to 1.10 mV at 1-sigma at the operating clock frequency of 3 GHz, and it consumes 54 μW/GHz after calibration.

Similar content being viewed by others

References

Pelgrom, M. J. M., Duinmaijer, A. C. J., & Weblbers, A. P. G. (1995). Matching properties of MOS transistors. IEEE Journal of Solid-State Circuits, 24(10), 1433–1439.

He, J., Sanyi, Z., Chen, D., & Geiger, R. L. (2009). Analyses of static and dynamic random offset voltages in dynamic comparators. IEEE Transactions on Circuits and Systems I: Regular Papers, 56, 911–919.

Nikoozadeh, A., & Murmann, B. (2006). An analysis of latch comparator offset due to load capacitor mismatch. IEEE Transactions on Circuits and Systems Part II: Express Briefs, 53(12), 1398–1402.

Figueiredo, P. M., & Vital, J. C. (2006). Kickback noise reduction techniques for CMOS latched comparator. IEEE Transactions on Circuits and Systems, 53(7), 541–545.

Murmann, B., et al. (2006). Impact of scaling on analog performance and associated modeling needs. IEEE Transactions on Electron Devices, 53(9), 2160–2167.

Miyahara, M., Asada, Y., Daehwa, P., & Matsuzawa, A. (2008). A low-noise self-calibrating dynamic comparator for high-speed ADCs. In Proc. A-SSCC, Nov 2008, pp. 269–272.

Miyahara, M., et al. (2009). A low-offset latched comparator using zero-static power dynamic offset cancellation technique. In IEEE A-SSCC, Taiwan, pp. 233–236.

Wong, J., et al. (2004). Offset compensation in comparators with minimum input-referred supply noise. In IEEE JSSC, May 2004, pp. 837–840.

Kobayashi, T., Nogami, K., Shirotori, T., & Fujimoto, Y. (1993). A current-controlled latch sense amplifier and a static power-saving input buffer for low-power architecture. IEEE Journal of Solid-State Circuits, 28, 523–552.

Wicht, B., Nirschl, T., & Schmitt-Landsiedel, D. (2004). Yield and speed optimization of a latch-type voltage sense amplifier. IEEE Journal of Solid-State Circuits, 39, 1148–1158.

Schinkel, D., Mensink, E., Kiumperink, E., van Tuijl, E., & Nauta, B. (2007). A double-tail latch-type voltage sense amplifier with 18 ps setup + hold time. In ISSCC Dig. Tech. Papers, Feb 2007, pp. 314–315 and 605.

Jeon, H. J., & Kim, Y.-B. (2010). A low-offset high-speed double-tail dual-rail dynamic latched comparator. In ACM GLSVLSI, Providence, May 2010.

van Elzakker, M., van Tuijl, A. J. M., Geraedts, P. F. J., Schinkel, D., Klumperink, E. A. M., & Nauta, B. (2008). A 1.9 μW 4.4fJ/conversion-step 10b 1MS/s charge-redistribution ADC. In ISSCC Dig. Tech. Papers, Feb 2008, pp. 244–245.

Razavi, B. (1995). Principles of data conversion system design. Piscataway, NJ: IEEE Press.

Van der Plas, G., Decoutere, S., & Donnay, S. (2006). A 0.16 pJ/conversion-step 2.5 mW 1.25 GS/S 4b ADC in a 90 nm digital CMOS process. In IEEE ISSCC Dig. Tech. Papers, Feb 2006, pp. 566–567.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Jeon, H., Kim, YB. A novel low-power, low-offset, and high-speed CMOS dynamic latched comparator. Analog Integr Circ Sig Process 70, 337–346 (2012). https://doi.org/10.1007/s10470-011-9687-5

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-011-9687-5