Abstract

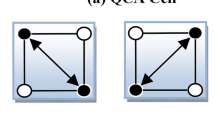

Nanotechnologies, remarkably Quantum-dot Cellular Automata (QCA), offer an attractive perspective for future computing technologies. In this paper, QCA is investigated as an implementation method for designing area and power efficient reversible logic gates. The proposed designs achieve superior performance by incorporating a compact 2-input XOR gate. The proposed design for Feynman, Toffoli, and Fredkin gates demonstrates 28.12, 24.4, and 7% reduction in cell count and utilizes 46, 24.4, and 7.6% less area, respectively over previous best designs. Regarding the cell count (area cover) that of the proposed Peres gate and Double Feynman gate are 44.32% (21.5%) and 12% (25%), respectively less than the most compact previous designs. Further, the delay of Fredkin and Toffoli gates is 0.75 clock cycles, which is equal to the delay of the previous best designs. While the Feynman and Double Feynman gates achieve a delay of 0.5 clock cycles, equal to the least delay previous one. Energy analysis confirms that the average energy dissipation of the developed Feynman, Toffoli, and Fredkin gates is 30.80, 18.08, and 4.3% (for 1.0 E k energy level), respectively less compared to best reported designs. This emphasizes the beneficial role of using proposed reversible gates to design complex and power efficient QCA circuits. The QCADesigner tool is used to validate the layout of the proposed designs, and the QCAPro tool is used to evaluate the energy dissipation.

Similar content being viewed by others

References

Lent, C.S., Tougaw, P.D., Porod, W., Bernstein, G. H.: Quantum cellular automata. Nanotechnology 4(1), 49 (1993)

Lent, C.S., Tougaw, P.D.: A device architecture for computing with quantum dots. Proc. IEEE 85, 541–557 (1997)

Landauer, R.: Irreversibility and heat generation in the computational process. IBM J. Res. Dev. 5, 183–191 (1961)

Bennett, C.H.: Logical reversibility of computation. IBM J. Res. Dev. 17, 525–532 (1973)

Abdullah-Al-shafi, M., Islam, M.S., Bahar, A.N.: A review on reversible logic gates and it’s QCA implementation. Int. J. Comput. Appl. 128(2), 27–34 (2015)

Mohammadi, Z., Mohammadi, M.: Implementing a one-bit reversible full adder using quantum-dot cellular automata. Quantum Inf. Process. 13, 2127–2147 (2014)

Das, J.C., De, D.: Reversible binary to grey and grey to binary code converter using QCA. IETE J. Res. 61(3), 223–229 (2015)

Das, J.C., De, D.: Reversible comparator design using quantum dot-cellular automata. IETE J. Res. 62(3), 323–330 (2016)

Das, J.C., De, D.: Novel low power reversible binary incrementer design using quantum-dot cellular automata. Microprocess. Microsyst. 42, 10–23 (2016)

Singh, G., Sarin, R.K., Raj, B.: Design and analysis of area efficient QCA based reversible logic gates. Microprocess. Microsyst. 52, 59–68 (2017)

Chabi, A.M., Roohi, A., Khademolhosseini, H., Sheikhfaal, S.: Towards ultra-efficient QCA reversible circuits. Microprocess. Microsyst. 49, 127–138 (2017)

Sasamal, T.N., Singh, A.K., Mohan, A.: Efficient design of reversible ALU in quantum-dot cellular automata. Int. J. Light Electron. Opt. 127(15), 6172–6182 (2016)

Sasamal, T.N., Singh, A.K., Ghanekar, U.: Design of non-restoring binary array divider in majority logic-based QCA. Electron. Lett. 52, 2001–2003 (2016)

Rad, S.K., Heikalabad, S.R.: Reversible flip-flops in quantum-dot cellular automata. Int. J. Theor. Phys. 56, 2990–3004 (2017)

Barughi, Y.Z., Heikalabad, S.R.: A three-layer full adder/subtractor structure in quantum-dot cellular automata. Int. J. Theor. Phys. 56, 2848–2858 (2017)

Bahar, A. N., Waheed, S., Habib, M. A.: A novel presentation of reversible logic gate in Quantum-dot Cellular Automata (QCA). In: International Conference on Electrical Engineering and Information & Communication Technology, pp. 1–6. Dhaka (2014)

Debnath, B., Das, J. C., De, D.: Reversible logic-based image steganography using quantum dot cellular automata for secure nanocommunication. IET Circ. Dev. Syst. 11(1), 58–67 (2017)

Hennessy, K., Lent, C.S.: Clocking of molecular quantum-dot cellular automata. J. Vac. Sci. Technol. B 19, 1752–1755 (2001)

Feynman, R.P.: Quantum mechanical computers. Opt. News 11(2), 11–20 (1985)

Toffoli, T.: Reversible computing, Tech memo - MIT/LCS/TM-151, MITLab for Comp. Sci. (1980)

Fredkin, E., Toffoli, T.: Conservative Logic in Collision-Based Computing, pp 47–81. Springer, Berlin (2002)

Peres, A.: Reversible logic and quantum computers. Phys. Rev. A, Gen. Phys. 32(6), 3266–3276 (1985)

Parhami, B.: Fault-tolerant reversible circuits. In: Fortieth Asilomar Conference on Signals, Systems and Computers, ACSSC’06, pp. 1726–1729 (2006)

Schulhof, G., Walus, K., Jullien, G.A.: Simulation of random cell displacements in QCA. ACM J. Emerg. Technol. Comput. Syst. 3(1), 1–14 (2007)

Pudi, V, Sridharan, K.: Low complexity design of Ripple Carry and Brent–Kung Adders in QCA. IEEE Trans. Nanotechnol. 11(1), 105–119 (2012)

Walus, K., Dysart, T., Jullien, G., Budiman, R.: QCA designer: a rapid design and simulation tool for quantum-dot cellular automata. IEEE Trans. Nanotechnol. 3 (1), 26–29 (2004)

Srivastava, S., Asthana, A., Bhanja, S., Sarkar, S.: QCAPro—an error power estimation tool for QCA circuit design. In: IEEE International Symposium on Circuits and Systems, pp. 2377–2380 (2011)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Sasamal, T.N., Singh, A.K. & Ghanekar, U. Toward Efficient Design of Reversible Logic Gates in Quantum-Dot Cellular Automata with Power Dissipation Analysis. Int J Theor Phys 57, 1167–1185 (2018). https://doi.org/10.1007/s10773-017-3647-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10773-017-3647-5