Abstract

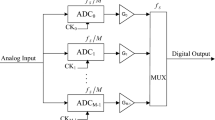

In time-interleaved analog-to-digital converter (ADC) architecture, offset mismatch, gain mismatch, and timing error between channels degrade the performance of time-interleaved ADCs. This paper focuses on the timing error, and proposes a simple calibration algorithm based on Hilbert transform estimate and then correct the timing error. With a cosine input, it could efficiently and accurately estimate the timing error. Fractional delay filters are developed to correct the timing errors. This simplifies the design and decreases the cost. Numerical simulations are used to verify the proposed estimation and correction algorithm.

Similar content being viewed by others

References

Black WC Jr, Hodges D (1980) Time interleaved converter arrays. IEEE J Solid State Circuits 15:1022–1029

Cheng-Chung H, Fong-Ching H, Chih-Yung S, Chen-Chih H, Ying-Hsi L, Lee C-C, et al (2007) An 11b 800MS/s Time-Interleaved ADC with Digital Background Calibration, in IEEE International Solid-State Circuits Conference, Digest of Technical Papers, pp 464–615

Chi Ho L, Hurst PJ, Lewis SH (2010) A four-channel time-interleaved ADC with digital calibration of interchannel timing and memory errors. IEEE J Solid State Circuits 45:2091–2103

Dyer KC, Fu D, Lewis SH, Hurst PJ (1998) An analog background calibration technique for time-interleaved analog-to-digital converters. IEEE J Solid State Circuits 33:1912–1919

Elbornsson J, Eklund JE (2001) Blind estimation of timing errors in interleaved AD converters, in Proc. IEEE International Conference on Acoustics, Speech, and Signal Processing, pp 3913–3916 vol 6

Elbornsson J, Folkesson K, Eklund JE (2002) Measurement verification of estimation method for time errors in a time-interleaved A/D converter system, in Proc. IEEE International Symposium on Circuits and Systems, pp III-129-III-132 vol 3

Fu D, Dyer KC, Lewis SH, Hurst PJ (1998) A digital background calibration technique for time-interleaved analog-to-digital converters. IEEE J Solid State Circuits 33:1904–1911

Gupta SK, Inerfield MA, Jingbo W (2006) A 1-GS/s 11-bit ADC with 55-dB SNDR, 250-mW power realized by a high bandwidth scalable time-interleaved architecture. IEEE J Solid State Circuits 41:2650–2657

Huang S, Levy BC (2007) Blind calibration of timing offsets for four-channel time-interleaved ADCs. IEEE Trans Circuits Syst I: Regular Papers 54:863–876

Huawen J, Lee EKF (2000) A digital-background calibration technique for minimizing timing-error effects in time-interleaved ADCs. IEEE Trans Circuits Syst II: Analog Digital Signal Process 47:603–613

Jamal SM, Fu D, Chang NCJ, Hurst PJ, Lewis SH (2002) A 10-b 120-Msample/s time-interleaved analog-to-digital converter with digital background calibration. IEEE J Solid State Circuits 37:1618–1627

Jamal SM, Fu D, Singh MP, Hurst PJ, Lewis SH (2004) Calibration of sample-time error in a two-channel time-interleaved analog-to-digital converter. IEEE Trans Circuits Syst I: Regular Papers 51:130–139

Jenq YC (1990) Digital spectra of nonuniformly sampled signals: a robust sampling time offset estimation algorithm for ultra high-speed waveform digitizers using interleaving. IEEE Trans Instrum Meas 39:71–75

Kurosawa N, Kobayashi H, Maruyama K, Sugawara H, Kobayashi K (2001) Explicit analysis of channel mismatch effects in time-interleaved ADC systems. IEEE Trans Circuits Syst I: Fundam Theory Appl 48:261–271

Munkyo S, Rodwell MJW, Madhow U (2005) Comprehensive digital correction of mismatch errors for a 400-msamples/s 80-dB SFDR time-interleaved analog-to-digital converter. IEEE Trans Microwave Theory Tech 53:1072–1082

Pan H, Tian S, Ye P (2010) An adaptive synthesis calibration method for time-interleaved sampling systems. Metrol Meas Syst XVII:405–414

Pereira JMD, Girao PMBS, Serra AMC (2004) An FFT-based method to evaluate and compensate gain and offset errors of interleaved ADC systems. IEEE Trans Instrum Meas 53:423–430

Vogel C (2005) The impact of combined channel mismatch effects in time-interleaved ADCs. IEEE Trans Instrum Meas 54:415–427

Acknowledgments

This work was supported by the National Natural Science Foundation of China (No.61301263), the Specialized Research Fund for the Doctoral Program of Higher Education of China (No.20120185130002), and the Fundamental Research Fund for the Central University of China (A03007023801217) and (A03008023801080).

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: V. D. Agrawal

Rights and permissions

About this article

Cite this article

Wang, L., Guo, L., Jiang, J. et al. A Hilbert-Transform-Based Method to Estimate and Correct Timing Error in Time-Interleaved ADCs. J Electron Test 31, 291–299 (2015). https://doi.org/10.1007/s10836-015-5523-7

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-015-5523-7