Abstract

The ever improving cost advantages and processing capabilities of the technology have been happening according to the so-called Moore’s Law. Although digital circuits can significantly benefit from the aggressive scaling, it is very controversial for analog circuit. However, analog circuit still has to follow the scaling trend because a single chip integration offers key commercial advantages. To optimally achieve the best performance/power/cost tradeoff with deeply scaled technology nodes, there is a clear trend and paradigm shift towards digital intensive and digitally assisted transceivers. Successes of such transceivers have been proven for individual transceiver components and narrow band systems. When targeting emerging communication standards, higher carrier frequencies, further technology scaling and reconfigurable radios, required signal processing design and implementation are orders of magnitudes more challenging but potential gains are promising. Based on a variety of transceiver designs implementing emerging architectures for different sub-6 GHz and 60 GHz communication systems, we will highlight the key challenges and opportunities experienced using 40 nm and 28 nm technology nodes.

Similar content being viewed by others

References

Lee, K., Nam, I., Kwon, I., Gil, J., Han, K., Park, S., Seo, B.I. (2005). The impact of semiconductor technology scaling on cmos rf and digital circuits for wireless application. IEEE Transactions on Electron Devices, 52(7), 1415–1422.

Murmann, B. (2006). Digitally assisted analog circuits. IEEE Micro, 26(2), 38–47.

Staszewski, R., Muhammad, K., Leipold, D., Hung, C.-M., Ho, Y.C., Wallberg, J., Fernando, C., Maggio, K., Staszewski, R., Jung, T., Koh, J., John, S., Deng, I. Y., Sarda, V., Moreira-Tamayo, O., Mayega, V., Katz, R., Friedman, O., Eliezer, O., Obaldia, E. de , Balsara, P. (2004). All-digital tx frequency synthesizer and discrete-time receiver for bluetooth radio in 130nm cmos. IEEE Journal of Solid-State Circuits, 39(12), 2278–2291.

Dabrowski, J., & Ramzan, R. (2010). Built-in loopback test for ic rf transceivers. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 18 (6), 933–946.

Staszewski, R., Staszewski, R., Jung, T., Murphy, T., Bashir, I., Eliezer, O., Muhammad, K., Entezari, M. (2010). Software assisted digital rf processor for single-chip gsm radio in 90nm cmos. IEEE Journal of Solid-State Circuits, 45 (2), 276–288.

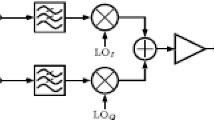

Borremans, J., Mandal, G., Giannini, V., Debaillie, B., Ingels, M., Sano, T., Verbruggen, B., Craninckx, J. (2011). A 40 nm cmos 0.4-6ghz receiver resilient to out-of-band blcokers. IEEE Journal of Solid-State Circuits, 46 (7), 1659–1671.

Craninckx, J. (2012). Cmos software-defined radio transceivers: Analog design in digital technology. IEEE Communications Magazine, 50 (4), 136–144.

Giannini, V., Nuzzo, P., Soens, C., Vengattaramane, K., Steyaert, M., Ryckaert, J., Goffioul, M., Debaillie, B., Van Driessche, J., Craninckx, J., Ingels, M. (2009). A 2mm2 0.1to-5ghz sdr receiver in 45nm digital cmos. In Solid-state circuits conference -digest of technical papers (ISSCC) (pp. 408-409). IEEE International.

Wickert, M., Mayer, U., Ellinger, F. (2012). 802.11a compliant spatial diversity receiver ic in bicmos. IEEE Transactions on Microwave Theory and Techniques, 60 (4), 1097–1104.

Vidojkovic, V., Szortyka, V., Khalaf, K., Mangraviti, G., Brebels, S., Thillo, W. v., Vaesen, K., Parvais, B., Issakov, V., Libois, M., Matsuo, M., Long, J., Soens, C., Wambacq, P. (2013). A low-power radio chipset in 40nm lp cmos with beamforming for 60ghz high-data-rate wireless communication. In Solid-state circuits conference digest of technical papers (ISSCC) (pp. 236-237). IEEE International.

Cha, H.-K., Song, S.-S., Kim, H.-T., Lee, K. (2008). A cmos harmonic rejection mixer with mismatch calibration circuitry for digital tv tuner applications. IEEE Microwave and Wireless Components Letters, 18 (9), 617–619.

Klumperink, E., Shrestha, R., Mensink, E., Wienk, G., Ru, Z., Nauta, B. (2007). Multipath polyphase circuits and their application to rf transceivers. In IEEE international symposium on circuits and systems (ISCAS) (pp. 273-276).

Tang, A., Hsiao, F., Murphy, D., Ku, I.-N., Liu, J., DSouza, S., Wang, N.-Y., Wu, H., Wang, Y.-H., Tang, M., Virbila, G., Pham, M., Yang, D., Gu, Q., Wu, Y.-C., Kuan, Y.-C., Chien, C., Chang, M. (2012). A low-overhead self-healing embedded system for ensuring high yield and long-term sustainability of 60ghz 4gb/s radio-on-a-chip. In Solid-state circuits conference digest of technical papers (ISSCC) (pp. 316-318). IEEE International.

Vidojkovic, V., Mangraviti, G., Khalaf, K., Szortyka, V., Vaesen, K., Van Thillo, W., Parvais, B., Libois, M., Thijs, S., Long, J., Soens, C., Wambacq, P. (2012). A low-power 57to-66ghz transceiver in 40nm lp cmos with -17db evm at 7gb/s. In Solid-state circuits conference digest of technical papers (ISSCC) (pp. 268-270). IEEE International.

Li, C., Li, M., Verhelst, M., Bourdoux, A., Borremans, J., Pollin, S., Chiumento, A., Van der Perre, L., Lauwereins, R. (2012). A generic framework for optimizing digital intensive harmonic rejection receivers. In IEEE workshop on signal processing systems (SiPS) (pp. 167-172).

Gaborieau, O., & et al. (2009). A SAW-less multiband WEDGE receiver. In IEEE ISSCC dig. tech. papers (pp. 114-115).

Sun, Y., & et al. (2010). A 50-300-MHz low power and high linear active RF tracking filter for digital TV tuner ICs. In IEEE custom integrated circuits conference (pp. 1-4).

Ru, Z., Moseley, N., Klumperink, E.A.M., Nauta, B. (2009). Digitally enhanced software-defined radio receiver robust to out-of-band interference. IEEE Journal of Solid-State Circuits, 44 (12), 3359–3375.

Li, C., & et al. (2013). Adaptive filter based low complexity digital intensive harmonic rejection for SDR receiver. In IEEE international conference on acoustics, speech and signal processing (ICASSP) (pp. 2712-2715).

Haykin, S. (2002). Adaptive filter theory. Upper Saddle River: Prentice Hall.

Balasubramanian, S., Boumaiza, S., Sarbishaei, H., Quach, T., Orlando, P., Volakis, J., Creech, G., Wilson, J., Khalil, W. (2012). Ultimate transmission. IEEE Microwave Magazine, 13 (1), 64–82.

Chen, W., & et al. (2010). A 60GHz-Band 22 Phased-Array Transmitter in 65nm CMOS. In Solid-state circuits conference digest of technical papers (ISSCC) (pp. 42-43). IEEE International.

Nariman, M., & et al. (2013). A compact millimeter-wave energy transmission system for wireless applications. In RFIC symposium (pp. 407-410).

IEEE Std 802.11a d TM- (2012).

Cong, Y., & et al. (2000). Switching sequence optimization for gradient error compensation in thermometer-decoded DAC arrays. IEEE Trans. on Circuits and Systems-II: Analog and digital signal processing, 47 (7), 585–595.

Geert, A.M., Van der Plas, et al. (1999). A 14-bit intrinsic Accuracy Q 2 random walk CMOS DAC. IEEE J. of Solid-state Circuits, 34 (12), 1708–1718.

Li, C., & et al. (2012). Efficient self-correction scheme for static non-idealities in nano-scale quadrature digital RF transmitters. In IEEE workshop on signal processing systems (SIPS) (pp. 71-76).

Lu, C., Wang, H., Peng, C. H., Goel, A., Son, S. W., Liang, P., Niknejad, A., Hwang, H. C., Chien, G. (2012). A 24.7dbm all-digital rf transmitter for multi-mode broadband applications in 40nm cmos. In Solid-state circuits conference digest of technical papers (ISSCC) (pp. 332-334) IEEE International.

Stothers, A.J. (2010). On the complexity of matrix multiplication. PhD Thesis, University of Edinburgh.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Li, C., Li, M., Khalaf, K. et al. Opportunities and Challenges of Digital Signal Processing in Deeply Technology-Scaled Transceivers. J Sign Process Syst 78, 5–19 (2015). https://doi.org/10.1007/s11265-014-0940-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11265-014-0940-x