Abstract

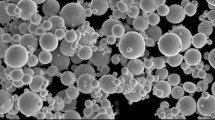

Pure Ni, the Ni-Cu alloy, and pure Cu layers as the under bump metallurgy (UBM) for a flip-chip solder joint were deposited by electrolytic plating. For the pure Ni layer, residual stress can be controlled by adding a wetting agent and decreasing current density, and it is always under tensile stress. The Ni-Cu alloys of different Cu compositions from ∼20wt.%Cu to 100wt.%Cu were deposited with varying current density in a single bath. The residual stress was a strong function of current density and Cu composition. Decreasing current density and increasing Cu content simultaneously causes the residual stress of the metal layers to sharply decrease. For the pure Cu layer, the stress is compressive. The Cu layer acts as a cushion layer for the UBM. The residual stress of the UBM strongly depends on the fraction of the Cu cushion layer. Interfacial reaction of the UBM with Sn-3.5 wt.% Ag was studied. As the Cu contents of Ni-Cu alloys increased, the dissolution rate increased. Several different intermetallic compounds (IMCs) were found. The lattice constants of alloys and the IMC increase with increasing Cu contents because the larger Cu atoms substitute for the smaller Ni atoms in the crystallites. The Cu content of the IMC are strongly dependent on the composition of the alloys. Ball shear tests were done with different metal-layer schemes. The failure occurs through the IMC and solder.

Similar content being viewed by others

References

V.P. Atluri, R.V. Mahajan, P.R. Patel, D. Mallik, J. Tang, V.S. Wakharkar, G.M. Chrysler, C.P. Chiu, G.N. Choksi, and R.S. Viswanath, MRS Bull. 28, 21 (2003).

T. Shimura, Y. Kawasaki, Y. Ohashi, K. Shirakawa, T. Hirose, S. Aoki, H. Someta, K. Makiyama, and S. Yokokawa, Proc. IEEE Radio Frequency Integrated Circuits (RFIC) Symp. (Piscataway, NJ: IEEE, 1998), pp. 25–28.

V.H. Ozguz and J. Yamaguchi, MRS Bull. 28, 35 (2003).

NCMS, Lead-Free Solder Project Final Report, NCMS Report 0401RE96 (Ann Arbor: MI: National Center for Manufacturing Sciences, 1997).

M.R. Harrison and J.H. Vincent, Proc. 12th Microelectronics and Packaging Conf.: IMAPS Europe (Cambridge, UK: IMAPS, 1999), pp. 98–106.

JEIDA, Report on Research and Development on Lead-Free Soldering (Tokyo: Japan Electronic Industry Development Association, 2000).

K. Zeng and K.N. Tu, Mater. Sci. Eng. R 38, 55 (2002).

M. Abtew and G. Selva-duray, Mater. Sci. Eng. R 27, 95 (2001).

J.H. Lau, Low Cost Flip Chip Technologies (New York: McGraw-Hill, 2000).

D.S. Patterson, P. Elenius, and J.A. Leal, “Wafer Bumping Technologies — A Comparative Analysis for Solder Deposition Processes and Assembly Considerations”, Kulicke & Soffa Technical Library, 2001, Web Site (www.kns.com).

D.S. Patterson, “Solder Bumping Step by Step”, Kulicke & Soffa Technical Library, 2001, Web Site (www.kns.com).

S.Y. Jang, J. Wolf, and K.W. Paik, J. Electron. Mater. 31, 478 (2002).

E.K. Yung and I. Turlik, IEEE Trans. CHMT 14, 549 (1991).

K.K. Yu and F. Tung, Proc. Electronic Manufacturing Technology Symp. (New York: IEEE, 1993), pp. 277–281.

H. Ezawa, M. Miyata, and S. Honma, Proc. 50th Electronic Components Technology Conf. (Piscataway, NJ: IEEE, 2000), pp. 1095–1100.

R. Kiumi, J. Yoshioka, F. Kuriyama, N. Saito, and M. Shimoyama, Proc. 52nd Electronic Components Technology Conf. (Piscataway, NJ: IEEE, 2002), pp. 711–716.

R.H. Esser, A. Dimoulas, N. Strifas, A. Christou, and N. Papanicolau, Microelectron. Reliab. 38, 1307 (1998).

H. Han, R. Boudreau, and S.-S. Tan, Proc. 46th Electronic Components Technology Conf. (Piscataway, NJ: IEEE, 1996), pp. 963–966.

D. Manessis, R. Patzelt, A. Ostmann, R. Aschenbrenner, and H. Reichl, Microelectron. Reliab. 44, 797 (2004).

D.R. Frear, J.W. Jang, J.K. Lin, and C. Zhang, JOM 53, 28 (2001).

P.A. Totta and R.P. Sopher, IBM J. Res. Dev. 13, 226 (1969).

G.Z. Pan, A.A. Liu, H.K. Kim, and K.N. Tu, Appl. Phys. Lett. 71, 2946 (1997).

J.O.G. Parent and D.D.L. Chung, J. Mater. Sci. 23, 2564 (1988).

P.L. Tu, Y.C. Chan, and J.K.L. Lai, IEEE Trans. CPMT B 20, 87 (1997).

W.G. Bader, Weld. Res. Suppl. Dec., 551s (1969).

S.K. Kang and V. Ramachandran, Scripta Metall. 14, 421 (1980).

P. Elenius, J. Leal, J. Ney, and D. Stepniak, Proc. 49th Electronic Components Technology Conf. (Piscataway, NJ: IEEE, 1999), pp. 260–265.

Y. Guo, S.M. Kuo, and C. Zhang, IEEE Trans. CPT 24, 655 (2001).

P. Elenius, Proc. 47th Electron. Components Technology Conf. (Piscataway, NJ: IEEE, 1997), pp. 248–253.

Integrated Circuit Engineering Corp., IC Packaging Update 1999 (Scottsdale, AZ: Integrated Circuit Engineering Corp., 1999).

S.K. Ghosh, A.K. Grover, G.K. Dey, and M.K. Totlani, Surf. Coating Technol. 126, 48 (2000).

E. Tóth-Kádár et al., J. Electrochem. Soc. 147, 3311 (2000).

G.G. Stoney, Proc. R. Soc. London A 82, 172 (1909).

S. Basrour and L. Robert, Mater. Sci. Eng. A 288, 270 (2000).

F.A. Lowenheim, Electroplating, 1st ed. (New York: McGraw-Hill, 1978).

J.K. Dennis and T.E. Such, Nickel and Chromium Plating, 3rd ed. (Cambridge, UK: Woodhead Pub., 1993).

A. Gangulee, Acta Metall. 22, 177 (1974).

N. Pangarov and R. Pangarova, J. Electroanal. Chem. 91, 173 (1978).

F. Spaepen, Acta Mater. 48, 31 (2000).

T.M. Korhonen, P. Su, S.J. Hong, M.A. Korhonen, and C.Y. Li, J. Electron. Mater. 29, 1194 (2000).

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Kim, S.H., Kim, J.Y., Yu, J. et al. Residual stress and interfacial reaction of the electroplated Ni-Cu alloy under bump metallurgy in the flip-chip solder joint. J. Electron. Mater. 33, 948–957 (2004). https://doi.org/10.1007/s11664-004-0021-1

Received:

Accepted:

Issue Date:

DOI: https://doi.org/10.1007/s11664-004-0021-1