Abstract

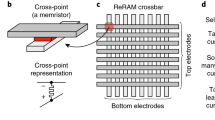

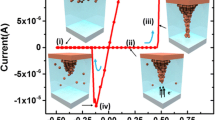

This work explores anti-serial (anti-parallel) memristive switches—ASMs (APMs)—as potential cross-point elements in nano-crossbar resistive random access memory arrays. The memory operation principles for both device combinations are shown in detail. The effectiveness of these memristive structures to the solution of the parasitic conducting (current sneak paths) problem is presented via an analytical approach which is based on the basic setup of resistive crossbar memories. Simulation results of crossbars of up to 4,096 elements, arranged in quadratic configurations, are conducted. The provided results supplement this comprehensive analysis of APMs and ASMs, outlining their overall performance characteristics and commenting on their applicability to the practical realization of large crossbar memory systems. Finally, a special array topology is applied to an ASM-based crossbar memory. Its performance is compared to the performance of the pure ASM-based memory. The conducted simulations reveal significantly improved read-out voltage margins which further contribute to addressing the parasitic current paths which prevent the reliable operation of memristive crossbar circuit topologies.

Similar content being viewed by others

References

Wright, C. D., Liu, Y., Kohary, K. I., Aziz, M. M., Hicken, R. J. (2011). Arithmetic and biologically-inspired computing using phase-change materials. Advanced Materials, 23, 3408–3413.

Waser, R. (2009). Resistive non-volatile memory devices (Invited Paper). Microelectronic Engineering, 7–9, 1925–1928.

Wong, H.-S. P., Lee, H.-Y., Yu, S., Chen, Y.-S., Wu, Y., Chen, P.-S., et al. (2012). Metal-Oxide RRAM. Proceedings of the IEEE, 6, 1951–1970.

Chua, L. O. (2011). Resistance switching memories are memristors. Applied Physics, 4, 765–783.

Chua, L. O. (1971). Memristor—the missing circuit element. IEEE Trans Circuit Theory, 18, 507–519.

Strukov, D. B., Snider, G. S., Stewart, D. R., Williams, R. S. (2008). The missing memristor found. Nature, 453, 80–83.

Sacchetto, D., Doucey, M.-A., De Micheli, G., Leblebici, Y., Carrara, S. (2011). New insight on bio-sensing by nano-fabricated memristors. BioNanoScience, 1–2, 1–3.

Vourkas, I., & Sirakoulis, G. C. (2013). Recent progress and patents on computational structures and methods with memristive devices. Recent Patents on Electrical & Electronic Engineering, 2, 101–116.

Erokhin, V., Berzina, T., Camorani, P., Smerieri, A., Vavoulis, D., Feng, J., et al. (2011). Material memristive device circuits with synaptic plasticity: learning and memory. BioNanoScience, 1–2, 24–30.

Howard, G., Gale, E., Bull, L., de Lacy, C. B., Adamatzky, A. (2012). Evolution of plastic learning in spiking networks via memristive connections. IEEE Trans Evolutionary Computation, 5, 711–729.

Erokhin, V., Howard, G. D., Adamatzky, A. (2012). Organic memristor devices for logic elements with memory. International Journal of Bifurcation and Chaos, 11, 1250283.

Manem, H., Rajendran, J., Rose, G. S. (2012). Design considerations for multilevel CMOS/nano memristive memory. ACM Journal on Emerging Technologies in Computing Systems, 1–6, 1–22.

Lehtonen, E., Poikonen, J. H., Laiho, M., Kanerva, P. (2013). Large-scale memristive associative memories. IEEE Transactions on Very Large Scale Integration (VLSI) Systems. doi:10.1109/TVLSI.2013.2250319.

Eshraghian, K., Cho, K.-R., Kavehei, O., Kang, S.-K., Abbott, D., Kang, S.-M. S. (2011). Memristor MOS content addressable memory (MCAM): hybrid architecture for future high performance search engines. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 8, 1407–1416.

Gaillardon, P.-E., Sacchetto, D., Beneventi, G. B., Ben Jamaa, M. H., Perniola, L., Clermidy, F., et al. (2013). Design and architectural assessment of 3-D resistive memory technologies in FPGAs. IEEE Transactions on Nanotechnology, 1, 40–50.

Hussaina, W., & Jahinuzzaman, S. M. (2012). A read-decoupled gated-ground SRAM architecture for low-power embedded memories. Integration, the VLSI Journal (Special Issue of GLSVLSI 2011: Current Trends on VLSI and Ultra Low-Power Design), 3, 229–236.

International Technology Roadmap for Semiconductors (2013) [Online]: http://www.itrs.net/ Accessed 24 December 2013.

Heath, J. R., Kuekes, P. J., Snider, G. S., Williams, R. S. (1998). A defect-tolerant computer architecture: opportunities for nanotechnology. Science, 280, 1716–1721.

Zidan, M. A., Fahmy, H. A. H., Hussain, M. M., Salama, K. N. (2013). Memristor-based memory: the sneak paths problem and solutions. Microelectronics Journal, 2, 176–183.

Lee, M.-J., Park, Y., Kang, B.-S., Ahn, S.-E., Lee, C. B., Kim, K., et al. (2007). 2-stack 1D–1R cross-point structure with oxide diodes as switch elements for high density resistance RAM applications (pp. 771–774). Washington, DC: IEEE Int Elec Dev Meeting (IEDM 2007).

Fei, W., Yu, H., Zhang, W., Yeo, K. S. (2012). Design exploration of hybrid CMOS and memristor circuit by new modified nodal analysis. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 6, 1012–1025.

Kim, K.-H., Gaba, S., Wheeler, D., Cruz-Albrecht, J. M., Hussain, T., Srinivasa, N., et al. (2012). A functional hybrid memristor crossbar-array/CMOS system for data storage and neuromorphic applications. Nano Letters, 1, 389–395.

Kim, S., Jeong, H. Y., Kim, S. K., Choi, S.-Y., Lee, K. J. (2011). Flexible memristive memory array on plastic substrates. Nano Letters, 12, 5438–5442.

Shin, J., Kim, I., Biju, K. P., Jo, M., Park, J., Lee, J., et al. (2011). TiO2-based metal—insulator—metal selection device for bipolar resistive random access memory cross-point application. Journal of Applied Physics, 3, 033712.

Linn, E., Rosezin, R., Kugeler, C., Waser, R. (2010). Complementary resistive switches for passive nanocrossbar memories. Nature Materials, 5, 403–406.

Liu, T., Kang, Y., Verma, M., Orlowski, M. K. (2012). Switching characteristics of antiparallel resistive switches. IEEE Transactions on Electron Devices Letters, 3, 429–431.

Vourkas, I., & Sirakoulis, G. C. (2012). A novel design and modeling paradigm for memristor-based crossbar circuits. IEEE Transactions on Nanotechnology, 6, 1151–1159.

Vourkas, I., Stathis, D., Sirakoulis, G. C. (2013). Improved read voltage margins with alternative topologies for memristor-based crossbar memories (pp. 364–367). Istanbul: Proc 21st IFIP/IEEE Int Conf Very Large Scale Integr (VLSI-SoC 2013).

Tappertzhofen, S., Linn, E., Nielen, L., Rosezin, R., Lentz, F., Bruchhaus, R., et al. (2011). Capacity based nondestructive readout for complementary resistive switches. Nanotechnology, 39, 395203.

Vourkas, I., & Sirakoulis, G. C. (2013). On the analog computational characteristics of memristive networks in 2013 (pp. 309–312). Abu Dhabi: IEEE Int Conf Electronics, Circuits, and Systems (ICECS 2013).

Pershin, Y. V., & Di Ventra, M. (2011). Memory effects in complex materials and nanoscale systems. Advances in Physics, 2, 145–227.

Mustafa, J., & Waser, R. (2006). A novel reference scheme for reading passive resistive crossbar memories. IEEE Transactions on Nanotechnology, 6, 687–691.

Flocke, A., & Noll, T. G. (2007). Fundamental analysis of resistive nano-crossbars for the use in hybrid nano/CMOS-memory (pp. 328–331). Munich: 33rd European Conf Solid State Circuits (ESSCIRC 2007).

Acknowledgments

This work was supported in part by a scholarship from the Bodossaki Foundation in Greece.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Vourkas, I., Sirakoulis, G.C. Nano-Crossbar Memories Comprising Parallel/Serial Complementary Memristive Switches. BioNanoSci. 4, 166–179 (2014). https://doi.org/10.1007/s12668-014-0132-y

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12668-014-0132-y