Abstract

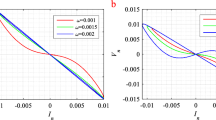

A chaotic noise is one of the most important implements for information processing such as neural networks. It has been suggested that chaotic neural networks have high performance ability for information processing. In this paper, we report two designs of a compact chaotic noise generator for large integration circuits using CMOS technology. The chaotic noise is generated using map chaos. We design both of the logistic map type and the tent map type circuits. These chaotic noise generators are compact as compared with the other circuits. The results show that the successful chaotic operations of the circuits because of the positive Lyapunov number. We calculate the Lyapunov exponents to certify the results of the chaotic operations. However, it is hard to estimate its accurate number for noisy data using the conventional method. And hence, we propose the modified calculation of the Lyapunov exponent for noisy data. These two circuits are expected to be utilized for various applications.

Similar content being viewed by others

References

K. Aihara, T. Takabe, and M. Toyoda, “Chaotic neural networks.” Phys. Rev. E 51, pp. 2693–2696, 1995.

K. Shimizu, K. Aihara, and M. Kotani, “An electrical circuit model of chaotic neural networks.” IEICE Trans. J73-A(3), pp. 495–508, 1990.

N. Kanou, Y. Horio, K. Aihara, and S. Nakamura, “A current-mode circuit of a chaotic neuron model.” IEICE Trans. Fundamentals E76-A(4), pp. 642–644, 1993.

Y. Hayakawa, A. Marumoto, and Y. Sawada, “Effect of the noise on the performance of a neural network model for optimization problems.” Phys. Rev. E 51, pp. 2693–2696, 1995.

M. Inoue and A. Nagaoshi, “A chaos neuro-computer.” Phys. Lett. A 158, pp. 373–376, 1991.

M. Inoue and S. Fukushima, “A neural network of chaotic oscillators.” Prog. Theor. Phys. 87(3), pp. 771–774, 1993.

T. Matsumoto, L. O. Chua, and R. Tokunaga, “Chaos via torus breakdown.” IEEE Trans. Circuit. Syst. CAS-34(3), pp. 240–254, 1987.

A. R-Vazque and M. D-Restituo, “CMOS design of chaotic oscillators using state variables: a monolithic Chua's circuit.” IEEE Trans. Circuit. Syst. 40(10), pp. 596–613, 1993.

J. M. Cruz and L. O. Chua, “An IC chip of Chua's circuit.” IEEE Trans. Circuits. Syst. 40(10), pp. 614–625, 1993.

T. Yamakawa, T. Miki, and E. Uchino, “A chaotic chip for analyzing nonlinear discrete dynamical network systems.” Proc. 2nd International Conference on Fuzzy Logic and Neural Networks, pp. 563–566, 1992.

C.-K. Pham, M. Tanaka, and K. Shono, “Chaotic behavior in simple looped MOS inverter.” IEICE Trans. E78-A(3), pp. 291–299, 1995.

H. Tanaka, S. Sato, K. Nakajima, E. Belhaire, and P. Garda, “Designs of integrated circuit to generate map chaos.” 1997 International Symposium on Nonlinear Theory and its Applications (NOLTA '97) 1, pp. 837–876, 1997.

M. A. van Wyk and W.-H. Steeb, Chaos in electronics. Kluwer Academic Publishers, Boston, 1997.

T. Delbruck, “Bump circuits for computing similarity and dissimilarity of analog voltage.” IEEE International Joint Conference on Neural Networks I, pp. 475–479, 1991.

M. Sano and Y. Sawada, “Measurement of the Lyapunov spectrum from a chaotic time series.” Phys. Rev. Lett. 55, pp. 1082–1085, 1985.

G. E. Hinton and T. J. Sejnowski, “Learning and relearning in Boltzmann machines,” in Parallel Distributed Processing, Chapter 7. MIT Press, Cambridge, MA, pp. 282–317, 1986.

M. Ito, H. Murakami, and L. O. Chua, “Communication systems via chaotic modulations.” IEICE Trans. Fundamentals E77-A(6), pp. 1000–1006, 1994.

I. Sasaki and K. Aoki, “A generating method of spread spectrum codes by chaos.” IEICE Trans. J79-B-I(8), pp. 582–584, 1996.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Tanaka, H., Sato, S. & Nakajima, K. Integrated Circuits of Map Chaos Generators. Analog Integrated Circuits and Signal Processing 25, 329–335 (2000). https://doi.org/10.1023/A:1008390217331

Issue Date:

DOI: https://doi.org/10.1023/A:1008390217331