Abstract

In this work, we aim to use the optical amplifiers, directional couplers and phase modulators to build the electro-optical gates. Thanks to the 2-layer-multilayer-perceptron structure, the inversion of matrix is performed to obtain the coupling ratio of the directional couplers and the phase delay of the phase modulators. The electro-optical OR, AND, XOR, NAND, NOR and XNOR gates are demonstrated. Moreover, we not only study the results under the ideal condition of device, but also discuss the imperfect situation with 1% error of fabrication or operation to study the tolerance of this system. Through our simulation results, the visibility of the gate output can be higher than 0.83. The gates can be fabricated in a silicon-based chip to develop the integrated optics computing system.

Similar content being viewed by others

Introduction

Optical computing is a striking issue in recent years. The logic gates are the fundamental devices to carry out this task1. All-optical logic gates based on photonic crystal (PC) waveguides, and ring resonators were proposed recently2,3,4. Also, there are many all-optical structures proposed to demonstrate the all-optical reservoir computing devices5,6,7,8. Thanks to the progress of the photonic technology which have been investigated intensively in recent decades, we can make these devices as a tiny chip9,10,11,12. Moreover, the temporal solitons and the continuous-wave light sources were used as the carriers of the input and output signals. The refractive index change of the waveguide by means of non-linear Kerr effect with high power light beam produces the tuning or switching of the output states of logic gates13,14. However, a long propagation path around several micrometers or even millimeters through the dielectric waveguides to deliver the light from light source to the logic gates might not be avoidable in a dielectric material (such as silicon) chip. The light might be absorbed by the waveguides leading to the deformation of the solitons. The low absorption and dispersion waveguides such as the hollow waveguide or using 3-dimensional PC structure over the waveguide might be considered to connect the light sources and the logic gates as well as to connect between the logic gates15,16,17.

Active components such as a tri-mode laser, Fabry–Perot laser, and semiconductor saturable absorber had also been proposed to form the all-optical logic gates14,18,19. Through tuning the optical injection of the tri-mode lasers, the change of logical state can be achieved14. High-speed all-optical logic gates at the bit rate of 340 Gb/s using the cross-gain modulation in semiconductor optical amplifier has also been achieved19.

Recently, researchers proposed the logic gates which are formed by microring/microdisk modulator20,21. Although the microring-/microdisk-modulators are tinier than our logic gate, the control process is more complicated than our design. With regard to the microring-modulator logic gates, they can achieve only AND, OR and XOR gates20. However, they need to modify the optical structure to carry out the corresponding function. In our study, we only need to tune the coupling ratio of the directional couplers and the phase of the phase shifter to achieve 6 logic gates at the single output port. For microdisk-modulator logic gates, the authors also can achieve OR, NOR, XNOR, XOR, AND and NAND logic gates21. However, the tunable laser providing 3 different wavelengths should be used. The size of the laser source and the external cavity to tune the wavelength might occupy several hundred square micrometers or even several square millimeters. The dimension of the integrated chip could be similar to that of our design.

In our previous work, we took advantage of the reservoir computing (RC) and unsupervised learning method optical neuron networks to establish an XOR gate5. This XOR gate with low bit error ratio was obtained by scanning the delay of optical phase shifter. In the present work, an electro-optical (EO) logic gates based on RC without the recurrent property are proposed. Obviously, it is a 2-layer-multilayer-perceptron (2-layer MLP) structure. This logic gates are composed of the optical amplifiers, directional couplers (DCs), and phase modulators (PMs). Comparing this new logic gates to our previous works, the feedback signal (the recurrent property) is removed in this new design. The switching time between 0 and 1 for the output of the gates can be shortened. In this work, the matrix inversion is performed to calculate the coupling ratio of the DCs and the phase delay of the PMs using the target output of the logic gates in the same optical configuration. The reconfigurable electro-optical OR, AND, XOR, NAND, NOR and XNOR gates formed by one optical structure are demonstrated.

Design of the 2-layer-multilayer-perceptron structure

It is known that RC system has been extensively used in the development of logic gates, waveform recognition, and rainfall prediction5,22,23,24. This system is composed of the input weight matrix \({W}^{in}\), the recurrent weight matrix \(W\), and the readout matrix \({W}^{out}\). The input matrix \({W}^{in}\) is used to scale the size of the input data to the size of the matrix W. The value of the elements in Win and W is chosen randomly. In this study, the learning is completed in a single pass-through training data. The optimal readout matrix \({W}^{out}\) is used to generate the output of the RC system.

In RC system, the neuron can be described as a function of the current input and its previous calculation result which can be expressed by25

where the function f is the nonlinear activation function of the neuron. Usually, the hyperbolic tangent function, tanh(), is used as the nonlinear activation function to converge the output value of neuron within − 1 and 126. In this research, the non-linear function of our optical neuron is provided by the optical amplifiers. (The optical setup is shown in Fig. 1.) \(L\) is the leaky rate which is a real number from 0 to 1. However, since we do not use the recurrent property of RC in the optical neural network, L and W are set to be 1 and null, respectively producing a 2-layer MLP structure. \(u\left(n\right)\) represents the n-th input data. Thus, the reservoir activation state, \(X\left(n\right)\), is modified to \(f\left({{\varvec{W}}}^{in}u\left(n\right)\right)\). The network target output \({Y}^{target}\) is given by

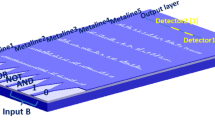

The optical setup of this EO logic gate. CW, DC and PM stand for the continuous wave, the 2 by 2 directional coupler, and the phase modulator. The possible recombination of the input signals A and B is (0, 0), (0, 1 V), (1 V, 0) and (1 V, 1 V). The corresponding Ytarget for the XOR gate is [0 1 1 0].

In Eq. (3), M and N are the number of the neurons and the number of the input data, respectively. By collecting the training data \(X\) and the target training signals \({Y}^{target}\), the readout matrix \({W}^{out}\) can be obtained by inversing the matrix X from Eq. (2).

The main feature of 2-layer MLP is the fact that the training (or the optimization) is done by dealing with the readout matrix \({W}^{out}\) using the inverse of the matrix X. As we mentioned above, once we obtain the elements of \({W}^{out}\), we could deduce the coupling ratio and phase in our DCs and PMs, respectively. This will be detailed in the next section. Through this method, we can obtain the parameters of the optical devices in this optical neural network.

Methods

Figure 1 illustrates the optical setup of our EO neural-network-based logic gates. The CW laser source at the wavelength of 1550 nm with the power of 0.1 W is launched into the DCin of our logic gate. The optical nonlinear effect of the optical fibers which connect the optical devices are ignored. This DCin with the coupling ratio of 50% is used to divide equally the input light into two light beams. The two light beams are launched into the two phase modulators (PMA and PMB in Fig. 1) individually. The half-wave voltage Vπ of the PMA and PMB is set randomly to be 1 V and 2 V, respectively. The input signals A and B are applied on the phase modulators PMA and PMB, respectively. The applied voltages are 0 or 1 V of the phase modulators to present the logic 0 and 1, respectively. PMA and PMB are connected to the directional coupler DCA. After that, the output signals of DCA are launched into DCB and DCC. DCA, DCB and DCC serve as the input matrix Win of the 2-layer MLP in which the values of the elements are chosen randomly. The coupling ratio of DCA, DCB and DCC is therefore set randomly. In our research, for the example of the XOR gate, the coupling ratios of the DCA, DCB and DCC are set randomly to be 0.56, 0.83 and 0.96, respectively.

The four outputs of the DCB and DCC are connected to the optical amplifiers A1, A2, A3 and A4, individually. The optical gain of the amplifiers is given by Go/(1 + G0P/Psat) where G0, P, Psat are the small signal power gain, the power of the input light, and the saturation output power, respectively. For all amplifiers, the small signal power gain and the saturation output power are set to be 30 dB and 30dBm, respectively. The optical amplifiers provide the non-linear function which is required for 2-layer MLP system. The complex electric field of the output light of the amplifiers A1, A2, A3 and A4 are denoted by X1, X2, X3 and X4, respectively, which are regarded as the output of the neurons. Therefore, the number of the neurons, M in Eqs. (3) and (4) is 4. In other words, an optical amplifier can be regarded as an optical neuron. The readout matrix \({W}^{out}\) is composed of the 3 phase modulators PM1, PM2 and PM3 as well as the 3 directional couplers DC1, DC2 and DC3. \({\varnothing }_{1}\), \({\varnothing }_{2}\) and \({\varnothing }_{3}\) are the phase delay of the phase modulators PM1, PM2 and PM3, respectively. \({\alpha }_{1}\), \({\alpha }_{2}\) and \({\alpha }_{3}\) are the coupling ratios of the DC1, DC2 and DC3, respectively. The general formula of the output of electric field for the phase modulator and the directional coupler can be given by Eqs. (6) and (7), respectively.

where \({X}_{in}\) and \({X}_{out}\) represent the complex input and output electric fields of the components, respectively. \(\varnothing\) and \(\alpha\) are the phase delay of the phase modulators and the coupling ratio of the 2 by 2 DCs, respectively. The two input lights in the directional coupler are interfered. Using Eqs. (6) and (7), the complex electric field of the output light of the whole system \({Y}^{target}\) can be derived by

The first step of the design process is to define the gate. For example, for an XOR gate, the possible recombination of the input signals A and B are (0, 0), (0, 1 V), (1 V, 0) and (1 V, 1 V). Thus, in Eq. (4), the number of the possible recombination of the input signals, \(N\), is 4. The corresponding result \({Y}^{target}\) for the XOR gate are [0 1 1 0]. The complex electric fields X1, X2, X3 and X4 are located at the output of A1, A2, A3 and A4, respectively, as shown in Fig. 1. For each recombination of the input signals, the complex values of X1, X2, X3 and X4 are collected to form the 4 by 4 matrix X of Eq. (4). According to Eq. (5), the values of \({w}_{1}\), \({w}_{2}\), \({w}_{3}\) and \({w}_{4}\) of the 1 by 4 matrix \({W}^{out}\) can be obtained using Ytarget and X. The coefficients of the terms X1, X2, X3 and X4 in Eq. (8) are equal to the 4 complex values \({w}_{1}\), \({w}_{2}\), \({w}_{3}\) and \({w}_{4}\) of \({W}^{out}\) forming 4 simultaneous equations. The phases of the complex numbers \({w}_{1}\), \({w}_{2}\), \({w}_{3}\) and \({w}_{4}\) are denoted by \({\theta }_{1}\), \({\theta }_{2}\), \({\theta }_{3}\) and \({\theta }_{4}\). The boundary conditions for \({\alpha }_{1}\), \({\alpha }_{2}\), \({\alpha }_{3}\), are real numbers between 0 and 1. By solving the simultaneous equations, \({\alpha }_{1}\), \({\alpha }_{2}\), \({\alpha }_{3}\), \({\varnothing }_{1}\), \({\varnothing }_{2}\) and \({\varnothing }_{3}\) can be obtained by

Results and discussion

The \({Y}^{target}\) for the OR, AND, XOR, NAND, NOR, XNOR logic gates is [0 1 1 1], [0 0 0 1], [0 1 1 0], [1 1 1 0], [1 0 0 0] and [1 0 0 1], respectively. For each gate, the coupling ratios of the DCA, DCB and DCC in Fig. 1, αA, αB and αC, are chosen randomly for 100 times to obtain the best tolerance. The detail calculation of tolerance will be discussed in the next section. The obtained αA, αB and αC for each gate are listed in Table 1. The corresponding coupling ratio of the directional couplers DC1, DC2, DC3 and the phase delay of the phase modulators PM1, PM2, PM3 calculated through Eqs. (2)–(14) are listed in Table 2. The output powers of the OR, AND, XOR, NAND, NOR and XNOR logic gates for different input signals A and B are shown in Fig. 2. For the electro-optical logic gates, the relation between the input signals and the output of the 2-layer MLP system follows the truth table of the corresponding logic gates. The reconfigurable logic gate can be achieved by tuning the parameters of the directional couplers27,28,29,30 and phase modulators31 as listed in Tables 1 and 2. It is worth mentioning that the phase delay of the phase modulators for NOR gate is close to null revealing that the phase modulators PM1, PM2 and PM3 might be removed. For the other gates, it is might be possible to find the solution to remove the phase modulators.

We use the visibility of the output signals of logic 0 and logic 1 to evaluate the tolerance of our logic gates. The definition of visibility is shown in Eq. (15)32

where \({I}_{min}^{1}\) and \({I}_{max}^{0}\) are the minimum light intensity of the high level (logic 1) and the maximum light intensity of the low level (logic 0), respectively. For example, for the output logic of XOR gate [0 1 1 0], if the output intensity of the 2-layer MLP system is [0.001, 0.013, 0.011, 0.002], we choose \({I}_{min}^{1}\) and \({I}_{max}^{0}\) as 0.011 and 0.002, respectively to calculate the visibility.

Since the coupling ratio of the directional couplers DC1, DC2, DC3 and the phase delay of the phase modulators PM1, PM2, PM3 are solved using Eqs. (2)–(14), the light intensity of the low level (logic 0) is null. The corresponding visibility of the output signals for all logic gates is unity.

During the fabrication of the directional couplers by optical fibers or by silicon waveguides, 1% error of the coupling ratio may happen. During the operation of the phase modulators by applying the voltage on the device, 1% error of the phase delay may occur. We calculate the visibility of the output signals as the coupling ratio of DC1, DC2, DC3 and the phase delay of the phase modulators PM1, PM2, PM3 are increased with 1% error. For example, for XOR gate, α1 obtained from Eq. (9) is 49% as listed in Table 2. As α1 is increased from 49 to 50% (αA, αB, αC, α2, α3, ϕ1, ϕ2 and ϕ3 are left unchanged as listed in Tables 1 and 2), the visibility of the output signal is calculated to be 0.99. For another example, for the XOR gate, as ϕ1 is increased from 8.88° to 12.48° (increasing 3.6° = 1% from – π to π), the visibility of the output signals is 0.91. For 100 calculations of different αA, αB, αC of each gates, the highest visibility of the 2-layer MLP system for all logic gates due to 1% error of the devices is listed in Table 3.

We can observe that for 1% error of the coupling ratio of the directional couplers DC1, DC2 and DC3, the worst visibility is 0.98. For 1% error of the phase delay of the phase modulators PM1, PM2 and PM3, the worst visibility is 0.83. It seems that the results could be acceptable showing that the reconfigurable optical logic gates can be achieved even with the fabrication or operation errors. In electronics, a flip-flop or latch is a circuit that can be used to store state information with a pair of cross-coupled NOR of NAND gates. The further application of the reconfigurable optical logic gates is to build the flip-flop. The optical memory could be realized.

Conclusion

In this work, we successfully establish an optical structure which can achieve EO logic gates. Thanks to this 2-layer-MLP structure, we can carry out the OR, AND, XOR, NAND, NOR and XNOR logic gates. In other words, we could take advantage of one optical neural network to achieve the most basic logic gates in optical approach. According to Eq. (5), we obtain the coupling ratio of the directional couplers DC1, DC2, and DC3 and the phase delay of the phase modulators PM1, PM2, PM3 under the ideal condition. The tolerance of the optical devices in our optical neural network is studied. The visibility changes of the output signals due to the 1% error during the fabrication and operation of the optical devices could be acceptable indicating that the reconfigurable optical logic gates can be realized in one optical configuration. Comparing our EO logic gates to the conventional electric logic gates, this EO logic gates have the capability of higher operating frequency, and high speed. In our study, the logic-gates functions among OR, AND, XOR, NAND, NOR and XNOR can be designed when the PMs and the coupling ratio of DCs are tuned in this EO logic gates. Thus, the control process is simpler. The present design uses the neural networks without recurrent property. The calculation performance could be faster than that of the previous work5. The optical logic gates can be applied to build an optical memory using the latch structure to store the information.

Data availability

The datasets used and/or analysed during the current study available from the corresponding author on reasonable request.

References

Saharia, A. et al. A comparative study of various all-optical logic. (ed. Janyani, V., Singh, G., Tiwari, M., & d’Alessandro, A.) 429–437 (Springer, 2019).

Selvakumari, M., Prabha, K. R., Robinson, S. & Batcha, A. S. Investigation on two dimensional photonic crystal based all optical logic gates. (ed. Zakaria, Z.& Emamian, S.S.) 129–142 (Springer, 2022).

Heydarian, K., Nosratpour, A. & Razaghi, M. Design and analysis of an all-optical NAND logic gate using a photonic crystal semiconductor optical amplifier based on the Mach–Zehnder interferometer structure. Photonics Nanostruct. Fundam. Appl. 49, 100992 (2022).

El Haffar, R., Mahboub, O., Farkhsi, A. & Figuigue, M. All-optical logic gates using a plasmonic MIM waveguide and elliptical ring resonator. Plasmonics 17, 831–842 (2022).

Lin, C. E. et al. All optical XOR logic gate formed by unsupervised optical neuron networks. Neurocomputing 460, 205–210 (2021).

Duport, F., Schneider, B., Smerieri, A., Haelterman, M. & Massar, S. All-optical reservoir computing. Opt. Express 20, 22783–22795 (2012).

Dejonckheere, A. et al. All-optical reservoir computer based on saturation of absorption. Opt. Express 22, 10868–10881 (2014).

Feldmann, J., Youngblood, N., Wright, C. D., Bhaskaran, H. & Pernice, W. H. P. All-optical spiking neurosynaptic networks with self-learning capabilities. Nature 569, 208–214 (2019).

Cai, D. P. et al. Compact pulley-type microring resonator with high quality factor. Appl. Phys. Express 7, 112202 (2014).

Cai, D. P. et al. High Q-factor microring resonator wrapped by the curved waveguide. Sci. Rep. 5, 10078 (2015).

Chiu, W. Y. et al. A photonic crystal ring resonator formed by SOI nano-rods. Opt. Express 15, 15500–15506 (2007).

Chen, C. C., Pertsch, T., Iliew, R., Lederer, F. & Tunnermann, A. Directional emission from photonic crystal waveguides. Opt. Express 14, 2423–2428 (2006).

Jandieri, V. et al. Functional all-optical logic gates for true time-domain signal processing in nonlinear photonic crystal waveguides. Opt. Express 28, 18317–18331 (2020).

Liu, J. C. et al. Numerical simulation of all-optical logic gates based on hybrid-cavity semiconductor lasers. J. Opt. Soc. Am. A 38, 808–816 (2021).

Lo, S. S., Wang, M. S. & Chen, C. C. Semiconductor hollow optical waveguides formed by omni-directional reflectors. Opt. Express 12, 6589–6593 (2004).

Chiu, H. K., Hsiao, F. L., Chan, C. H. & Chen, C. C. Compact and low-loss bent hollow waveguides with distributed Bragg reflector. Opt. Express 16, 15069–15073 (2008).

Chen, C. C., Tsai, Y. L., Hsu, C. L. & Chang, J. Y. Propagation loss reduction of photonic crystal slab waveguides by microspheres. Opt. Express 12, 3934–3939 (2004).

Nakarmi, B., Zhang, X. & Won, Y. H. All-optical 4x10 Gbps NAND gate using single mode Fabry–Pérot laser diode. Opt. Express 23, 26952–26961 (2015).

Pradhan, R. All-optical XNOR/NOT logic gates and LATCH based on a reflective vertical cavity semiconductor saturable absorber. Appl. Opt. 53, 3807–3813 (2014).

Ying, Z. et al. Automated logic synthesis for electro-optic logic-based integrated optical computing. Opt. Express 26, 28002–28012 (2018).

Gostimirovic, D. & Ye, W. N. Ultracompact CMOS-compatible optical logic using carrier depletion in microdisk resonators. Sci. Rep. 7, 1–10 (2017).

Cheng, T. Y., Chou, D. Y., Liu, C. C., Chang, Y. J. & Chen, C.-C. Optical neural networks based on optical fiber-communication system. Neurocomputing 364, 239–244 (2019).

Cheng, T. Y., Liu, C. C., Jhou, D. Y. & Chen, C. C. Impact of coupling topology upon noise robustness of small optical reservoirs. Sci. Rep. 10, 14086 (2020).

Yen, M. H., Liu, D. W., Hsin, Y. C., Lin, C. E. & Chen, C. C. Application of the deep learning for the prediction of rainfall in Southern Taiwan. Sci. Rep. 9, 12774 (2019).

Lukoševičius, M. A Practical Guide to Applying Echo State Networks (ed. Montavon, G., Orr, G. B. & Müller, K. R.) (Springer, 2012).

Lukoševičius, M., Jaeger, H. & Schrauwen, B. Reservoir computing trends. KI Künstliche Intelligenz 26, 365–371 (2012).

Orlandi, P. et al. Tunable silicon photonics directional coupler driven by a transverse temperature gradient. Opt. Lett. 38(6), 863–865. https://doi.org/10.1364/OL.38.000863 (2013).

Zhang, Q. et al. Reconfigurable directional coupler in lithium niobate crystal fabricated by three-dimensional femtosecond laser focal field engineering. Photon. Res. 7, 503–507 (2019).

Chen, C. C., Porte, H., Goedgebuer, J. P., Armbruster, V. & Ferriere, R. Adjustment of the coupling ratio by laser ablation of Ti:LiNbO3 directional couplers. Opt. Laser Technol. 34, 453–455 (2002).

Lo, S. S. & Chen, C. C. High finesse of optical filter by a set Fabry–Perot cavity. J. Opt. Soc. Am. B 24, 1853–1856 (2007).

Sorianello, V., Midrio, M. & Romagnoli, M. Graphene on SOI phase modulation. In 2015 Fotonica AEIT Italian Conference on Photonics Technologies. 1–3. https://doi.org/10.1049/cp.2015.0133 (2015).

Bahaa, M. C. T. & Saleh, E. A. Fundamentals of Photonics 2nd edn, 419–420 (Wiley, Hoboken, 2007).

Acknowledgements

The authors thank Taiwan Semiconductor Research Institute for the software support. This work was supported by Ministry of Science and Technology, Taiwan [Grant Numbers MOST 110-2112-M-008-032].

Author information

Authors and Affiliations

Contributions

C.-C.C. supervised this research topic. C.-E.L., Y.-H.L. and M.-T.Z. executed the simulation. Y.-H.L. and M.-T.Z. performed the simulation result. C.-C.C. and C.-E.L. analyzed the results and wrote this manuscript. All authors discussed and commented on the results and manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Lin, CE., Lu, YH., Zhou, MT. et al. Reconfigurable electro-optical logic gates using a 2-layer multilayer perceptron. Sci Rep 12, 14203 (2022). https://doi.org/10.1038/s41598-022-18408-0

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-022-18408-0

This article is cited by

-

Design and simulation of reconfigurable optical logic gates for integrated optical circuits

Optical and Quantum Electronics (2023)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.