Abstract

Topological insulators are unique electronic materials with insulating interiors and robust metallic surfaces. Device applications exploiting their remarkable properties have so far been hampered by the difficulty to electrically tune the Fermi levels of both bulk and thin film samples. Here we show experimentally that single-crystal nanowires of the topological insulator Bi2Se3 can be used as the conduction channel in high-performance field effect transistor (FET), a basic circuit building block. Its current-voltage characteristics are superior to many of those reported for semiconductor nanowire transistors, including sharp turn-on, nearly zero cutoff current, very large On/Off current ratio and well-saturated output current. The metallic electron transport at the surface with good FET effective mobility can be effectively separated from the conduction of bulk Bi2Se3 and adjusted by field effect at a small gate voltage. This opens up a suite of potential applications in nanoelectronics and spintronics.

Similar content being viewed by others

Introduction

Topological insulators (TI) are characterized as a new class of materials which have insulating band gaps in the bulk but gapless surface states topologically protected by time-reversal symmetry1,2. Recently discovered three-dimensional (3D) TI materials, such as Bi2Se3, Bi2Te3 and Sb2Te3, have been intensively investigated both theoretically and experimentally3,4. The gapless surface states featuring helical Dirac electrons have been observed by angle-resolved photoemission spectroscopy5,6,7 and scanning tunneling microscopic techniques8,9,10. Thin films and nanoribbons of TI show anomalous high-field magnetoresistance11,12,13, coherent surface transport induced by Aharonov-Bohm interference14 and optoelectronic properties due to the spin-polarized surface states15.

Bi2Se3, a well-known thermoelectric material, is a 3D TI with a bulk band gap of 0.35 eV and a single Dirac cone on the surface2,3. Most current experimental research focusses on the surface states of thin TI samples exfoliated from bulk material6,16. A few groups have reported modification of the surface conduction of such exfoliated TI samples by doping, applying a vertical electric field or polarized light15,17,18,19. Yet, up to now, no high-performance microelectric devices based on topological insulators such as the analog of metal oxide semiconductor field effect transistors (MOSFETs) have been reported. The MOSFET is the basic building block in complementary metal oxide semiconductor (CMOS) technology, the fundamental basis for digital and analog circuits. For conventional CMOS devices, the surface conduction of Si is protected by thermal SiO2 to optimize its inversion properties for good transistor performance. This is one of the primary reasons why Si is preferred over other semiconductor materials for CMOS technology. For a topological insulator material, the gapless surface state is derived from its inherent material properties and maintains a robust surface conduction. Therefore the integration of TI as the active conduction channel in MOSFETs is very attractive because it will leverage the advantages afforded by the novel TI materials with the vast infrastructure of current semiconductor technology.

In this work, we fabricated and measured surrounding-gate Bi2Se3 nanowire field-effect transistors. The nanowires were grown from Au catalyst and integrated by using a self-alignment technique. The FET current-voltage (I–V) characteristics were measured at different temperatures, exhibiting excellent performance. We have studied the separation of surface metallic conduction from bulk semiconductor conduction with gate electric field at different temperatures. The activation energy of bulk conduction was found to be very close to the band gap of bulk Bi2Se3. We have also studied the effective electron mobility and scattering mechanism in the devices.

Results

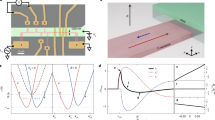

Figure 1 (a) shows a scanning electron microscopy (SEM) image of the as-synthesized Bi2Se3 nanowires which are about 50 nm to 150 nm wide and 10 μm long. Au nanoparticles (NPs) were found at the top-end of each nanowire. This indicated that Bi2Se3 vapor was first absorbed by Au catalyst to form a Bi2Se3 and Au eutectic; then Bi2Se3 diffused through Au to form the single-crystal nanowires. This process is similar to the growth of Si nanowires governed by vapor-liquid-solid (VLS) mechanism. Bi2Se3 has a layered rhombohedral crystal structure with five covalently bonded atoms in one unit cell. These quintuple layers are linked by van der Waals interactions20. The high-resolution transmission electron microscopy (HRTEM) image shown in Figure 1 (b) demonstrates that the Bi2Se3 nanowires are in a well-defined single-crystal rhombohedral phase and the growth direction is close to  . A schematic of the Bi2Se3 nanowire FET is shown in Figure 1(c) and a TEM image of the cross-section in Figure 1 (d). The hexagonal nanowire core is surrounded first by the insulating HfO2 layer and then by the Omega-shaped top gate.

. A schematic of the Bi2Se3 nanowire FET is shown in Figure 1(c) and a TEM image of the cross-section in Figure 1 (d). The hexagonal nanowire core is surrounded first by the insulating HfO2 layer and then by the Omega-shaped top gate.

The electrical characterization was carried out on a probe station inside a vacuum chamber. As shown in Figure 2 (a), the transistor has excellent drain current (IDS) vs. top gate voltage (VGS) transfer characteristics: cutoff current close to zero, strong-inversion-like on-state current and current on/off ratio larger than 108 at a VGS swing of 1.0 V. The backside Si was grounded during all the measurements. The transistor has unipolar current dominated by electron conduction. This is similar to a conventional long-channel Schottky-barrier MOSFET with either electron or hole conduction determined by the unipolar Schottky junctions at the source and drain. No hysteresis was observed in the IDS–VGS curves at 77 K. A hysteresis shift was observed at higher temperatures (T > 240 K), most likely due to the activation of traps in the HfO2. Very similar device characteristics were observed for the drain voltage (VDS) in the range 0.05 V to 4.0 V used in the study.

(a) Transfer characteristics (IDS-VGS) of Bi2Se3 nanowire FET at 77K; inset is the linear-scale plot showing Vth = −3.8 V. (b) and (c) are linear-scale and log-scale IDS-VDS for VGS from −4.4 V to −1.4 V at 77 K. (d) IDS as a function of over-threshold voltage (VGS-Vth) and inset: its linear fit slope vs. temperature.

As shown in Figure 2 (b) and (c), the Bi2Se3 nanowire FET exhibits well-saturated, smooth IDS vs. VDS curves with negligible contact resistance. The transistor output characteristics clearly demonstrate cutoff, weak, moderate and highly conductive regions at different VGS, similar to the cutoff (leakage), weak, moderate and strong inversion regions of conventional MOSFETs. IDS saturates roughly at VDS = VGS − Vth in the highly conductive region but does not saturate at VDS ≈ 3φt in the weak/moderate conductive regions (φt = kT/q). IDS keeps increasing significantly after 3φt. This means that the Bi2Se3 nanowire FET does not follow the diffusion current model as described for conventional MOSFETs. We believe IDS in the weak/moderate conductive regions is also dominated by drift current.

Similar IDS-VDS characteristics have been obtained at different temperatures. We observed that the saturation current IDsat at various VGS does not follow the quadratic law which predicts that IDsat varies linearly with (VGS-Vth)2 as it does in conventional long-channel MOSFETs. Rather, as shown in Figure 2(d), IDsat varies linearly with the over-threshold voltage (VGS-Vth) at different temperatures for VGS in the range −3.8 V to −1.4 V. The saturation current can be expressed by the drift current model as a product of the number of electrons and their velocity at the source end of the nanowire:

where A, ns, Cox, L and vs are nanowire cross-section area, electron concentration at source end, gate capacitance, channel length and electron velocity at the source end of Bi2Se3- nanowire, respectively. Therefore this linear relationship suggests that the saturation of IDS is due to electron velocity saturation at the source end of the channel instead of pinch-off at the drain end of the nanowire channel21. The slope of each IDsat vs. (VGS-Vth) curve is saturation channel conductance (gdsat); its value at different temperatures is extracted from Fig. 2 (d) and plotted in the inset, showing that the electron velocity at the source end increases linearly with decreasing temperature. The capacitance per unit length Cox/L = 1.3 × 10−9 F/m was given by numerical calculation using a Synopsis TCAD program based on the cross-section size of the TEM image in Figure 1 (d). The calculated value of vs is from 1 × 106 cm/s to 2 × 106 cm/s for temperatures from 240 K to 77 K, which is of the same order of magnitude as the Fermi velocity of Ti22 in the source and drain contacts.

Figure 3 (a) shows the electron effective mobility (μeff) of Bi2Se3 nanowire FET as a function of applied gate voltage at different temperatures. The field effect mobility extracted from the IDS-VGS curves shows a similar result. The effective mobility values were extracted from the linear region of IDS-VDS curves by using the following equation:

The electron effective mobility decreases with increasing gate voltage in the range 200 cm2/Vs to 1300 cm2/Vs at 77 K. It should be noted that the precision of effective mobility estimation can be affected by the numerically calculated gate capacitance due to the top and bottom gate coupling. In Figure 3 (b), electron effective mobility as a function of temperature at different gate voltages is plotted and fitted using μeff ~ Tα. The value of α is about −1.85 at small over-threshold voltage and increases to −1.0 at large over-threshold voltage. Larger over-threshold voltage will induce higher vertical electric fields. These mobility-temperature relationships suggest that electron-phonon scattering is a dominating factor in low-field conduction (optical phonon scattering for −2.0 > α > −1.5, acoustic phonon scattering for α ≈ −1.5) and as the gate electric field increases, interface charge Columbic scattering limits electron mobility in the Bi2Se3 nanowire FETs with α = −123.

Figure 4 (a) compares the transfer characteristics (IDS-VGS) of a Bi2Se3 nanowire FET at different temperatures, all of which show unipolar, n-type, field effect behaviors. The IDS-VGS curves obtained at temperatures lower than 240 K show a clear cutoff region (IDS ≈ 0) in the subthreshold region (VGS < Vth) and a large On/Off current ratio reaching 108. The Off-state current for temperatures > 240 K flattens and saturates at negative voltages much below Vth. The temperature dependence of currents in the On and Off states are summarized in Figure 4(b). The Off-state current for temperatures above 240 K was taken from the flat region while the On-state current was taken at VGS = 2.0 V. The Off state current starts increasing rapidly as the temperature increases above 240 K, while the On-state current keeps decreasing as the temperature increases. Such temperature dependence indicates metallic conduction in the On state and insulating behavior in the Off state. Figure 4(c) shows a fitting of the strongly activated temperature-dependent current to  where Ea is the activation energy, k is Boltzmann's constant and I0 is a constant prefactor. The fit shows that Ea is about 0.33 eV with uncertainty = 0.01 eV which is very close to reported bandgap value of bulk Bi2Se32,3.

where Ea is the activation energy, k is Boltzmann's constant and I0 is a constant prefactor. The fit shows that Ea is about 0.33 eV with uncertainty = 0.01 eV which is very close to reported bandgap value of bulk Bi2Se32,3.

(a) IDS-VGS at different temperature from 77 K to 295 K with VDS = 50 mV.(b) Data extracted from (a): On-state and Off-state current as a function of temperature. (c) ln(IDS) at Off state vs. 1/kT above 240 K and its fit to  . (d) Subthreshold slope as a function of temperature, its fit to

. (d) Subthreshold slope as a function of temperature, its fit to  and ideal subthreshold slope

and ideal subthreshold slope  which is defined by thermal emission.

which is defined by thermal emission.

Discussion

These results can be interpreted phenomenologically as follows. In the Off state, the gate voltage is large enough to deplete the electrons from the nanowire. The small, temperature dependent Off-state current is due to thermal excitations across the energy band gap of the bulk of Bi2Se3. It also indicates that the electric field generated by the gate voltage below the threshold is likely to be strong enough to modify the spectrum of the nanowire and destroy the surface conduction channels. Numerical simulation24 has demonstrated that electric field could drive a topological insulator across a quantum phase transition to become a trivial band insulator. In contrast to conventional semiconductor nanowires, the saturated current in the On-state is linear in gate voltage, indicating metallic conduction and is most likely flowing at the surface of the nanowire. This interpretation is also consistent with the temperature dependence of the saturated conductance. These two regimes, the surface metallic conduction and the insulating switch-off, can be controlled by a surprisingly small gate voltage (a few Volts). Our data cannot unambiguously confirm or rule out the presence of Helical Dirac fermions. Future spectroscopic experiments and theoretical simulations on the spectrum and transport properties of Bi2Se3 nanowire FETs will shed more light on the phenomena reported here.

The switching performance of a FET is characterized by its subthreshold swing (S) which is defined as the VGS swing to achieve 10 time increase of IDS in the subthreshold region. While these Bi2Se3 nanowire FETs have a larger S value than the ideal thermodynamic limit, it is still much smaller than those often reported for nanowire-FETs based on conventional semiconductors. Figure 4 (d) shows the subthreshold swing of the Bi2Se3 nanowire FET at different temperatures and its fit to:

where Cch-gnd is the capacitance between the nanowire surface and ground and Cit is interface state capacitance21,25. It should be noted that the effect of dielectric interface states is negligible at low temperature because IDS-VGS has almost zero hysteresis (see Fig. 2a). From the fitting which assumes Cch-gnd/Cox has no temperature dependence, Cch-gnd is about 0.56Cox or 7.3 × 10−10 F/m for the Bi2Se3 nanowire.

In summary, we have fabricated Bi2Se3 nanowire field-effect transistors by using a self-alignment technique and observed excellent device characteristics. The FETs show unipolar, n-type behavior with a clear cutoff in the Off state with only thermally activated conduction at relatively high temperatures and a well-saturated output current indicating surface metallic conduction. The effective mobility extracted for different gate voltages and temperatures indicates phonon scattering at low electric fields and surface Columbic scattering at larger electric fields. The achievement of sharp switching from Cutoff to surface conduction and saturation current by a gate voltage of a few volts is neither expected nor has been previously reported. The different scaling behavior of the saturation current versus gate voltage in these devices relative to most conventional semiconductor nanowire FETs may lead to novel circuit applications. Finally, since the spin and momentum are locked in the surface states of topological insulators3, our results open up the possibility of electric manipulation of spin current using gate voltage.

Methods

Bi2Se3 nanowire FETs were fabricated by using a self-alignment process, similar to the one used in our previous research on Si nanowire FETs26,27. The essential steps are as follows: first, a layer of thermal SiO2 (300 nm) was grown by dry oxidation on a Si wafer. On the top of the wafer, the Bi2Se3 nanowires were grown from Au catalyst deposited by sputtering in pre-defined locations. The nanowire growth followed a solid-vapor-solid route. The wafers (with Au) were loaded at the downstream end in a horizontal tube furnace while Bi2Se3 source powder was located at the heat center of the furnace. Then the furnace is heated to a temperature in a range of 500°C to 550°C and kept in that temperature for 2 h under a flow of 50 standard cubic centimeters (sccm) Ar as carrier gas. The as-grown Bi2Se3 nanowires were about 20 μm in length and 150 nm in diameter. Then Ti(3 nm)/Pt(100 nm) source/drain (S/D) electrodes were patterned on the nanowires at the growth location by photolithography, forming Pt/Bi2Se3 Schottky junctions at both source and drain. The channel length was defined to be 2 μm. A layer of 30-nm HfO2 was then deposited at 250°C by atomic layer deposition (ALD) with precursors of Tetrakis(ethylmethylamino)hafnium and water covering the nanowire channel and also part of S/D electrodes. The last step was the formation of a 100 nm Pd top gate by a lift-off process. Unlike the traditional nanowire harvesting and alignment methods, our self-alignment approach not only enables simultaneous batch fabrication of reproducible and homogeneous nanowire devices of high quality, but also limits the contamination of the nanowire during the fabrication process.

References

Bernevig, B. A., Hughes, T. L. & Zhang, S. C. Quantum spin hall effect and topological phase transition in HgTe quantum wells. Science 314, 1757–1761 (2006).

Zhang, H. et al. Topological insulators in Bi2Se3, Bi2Te3 and Sb2Te3 with a single Dirac cone on the surface. Nat. Phys. 5, 438–442 (2009).

Hasan, M. Z. & Kane, C. L. Colloquium: topological insulators. Rev. Mod. Phys. 82, 3045–3067 (2010).

Qi, X. L. & Zhang, S. C. Topological insulators and superconductors. Rev. Mod. Phys. 83, 1057–1110 (2011).

Hsieh, D. et al. A tunable topological insulator in the spin helical Dirac transport regime. Nature 460, 1101–1105 (2009).

Chen, Y. L. et al. Experimental realization of a three-dimensional topological insulator, Bi2Te3 . Science 325, 178–181 (2009).

Xia, Y. et al. Observation of a large-gap topological-insulator class with a single Dirac cone on the surface. Nat. Phys. 5, 398–402 (2009).

Hanaguri, T., Igarashi, K., Kawamura, M., Takagi, H. & Sasagawa, T. Momentum-resolved Landau-level spectroscopy of Dirac surface state in Bi2Se3 . Phys. Rev. B 82, 081305 (2010).

Roushan, P. et al. Topological surface states protected from backscattering by chiral spin texture. Nature 460, 1106–1109 (2009).

Zhang, T. et al. Experimental demonstration of topological surface states protected by time-reversal symmetry. Phys. Rev. Lett. 103, 266803 (2009).

Checkelsky, J. G. et al. Quantum interference in macroscopic crystals of nonmetallic Bi2Se3 . Phys. Rev. Lett. 103, 246601 (2009).

Kong, D. et al. Topological insulator nanowires and nanoribbons. Nano Lett. 10, 329–333 (2010).

Xiu, F. et al. Manipulating surface states in topological insulator nanoribbons. Nat. Nanotech. 6, 216–221 (2011).

Peng, H. et al. Aharonov–Bohm interference in topological insulator nanoribbons. Nat. Mater. 9, 225–229 (2010).

McIver, J. W., Hsieh, D., Steinberg, H., Jarillo-Herrero, P. & Gedik, N. Control over topological insulator photocurrents with light polarization. Nat. Nanotech. 7, 96–100 (2012).

Hsieh, D. et al. Observation of time-reversal-protected single-dirac-cone topological-insulator states in Bi2Te3 and Sb2Te3 . Phys. Rev. Lett. 103, 146401 (2009).

Kong, D. et al. Ambipolar field effect in the ternary topological insulator (BixSb1−x)2Te3 by composition tuning. Nat. Nanotech. 6, 705–709 (2011).

Steinberg, H., Gardner, D. R. Lee, Y. S. & Jarillo-Herrero, P. Surface state transport and ambipolar electric field effect in Bi2Se3 Nanodevices. Nano Lett. 10, 5032–5036 (2010).

Cho, S., Butch, N. P., Paglione, J. & Fuhrer, M. S. Insulating behavior in ultrathin bismuth selenide field effect transistors. Nano Lett. 11, 1925–1927 (2011).

Lind, H., Lidin, S. & Haussermann, U. Structure and bonding properties of (Bi2Se3)m(Bi2)n stacks by first-principles density functional theory. Phys. Rev. B 72, 184101 (2005).

Hu, C. Modern Semiconductor Devices for Integrated Circuits (Prentice Hall), 219–220.

Zhang, D. et al. Electronic transport properties of α-TiAl alloys. Int. J. Modern Phys. B 19, 3869–3895 (2005).

Joen, D. S. & Burk, D. E. MOSFET electron inversion layer mobilities – a physically based semi-empirical model for a wide temperature range. IEEE Trans. Elec. Dev. 36, 1456–1463 (1989).

Li, J. & Chang, K. Electric field driven quantum phase transition between band insulator and topological insulator. Appl. Phys. Lett. 95, 222110 (2009)

Frei, J. et al. Body effect in tri- and pi-gate SOI MOSFETs. IEEE Elec. Dev. Lett. 25, 813–815 (2004)

Li, Q. et al. The large-scale integration of high-performance silicon nanowire field effect transistors. Nanotechnology 20, 415202 (2009).

Zhu, X. et al. Fabrication, characterization and simulation of high performance Si nanowire-based non-volatile memory cells. Nanotechnology 22, 254020 (2011).

Acknowledgements

The work described here was supported by US NIST Grant 60NANB11D148, US NSF Grant ECCS-0846649 and Virginia Microelectronics Consortium Research Grant.

Author information

Authors and Affiliations

Contributions

H.Z. fabricated and measured the devices. H.Z. and Q.L. wrote the paper. H.Z., E.Z., H.-J.J., H.Y., H.L., O.K., C.A.R., D.E.I. and Q.L. contributed to the data analysis. J.E.B. carried out the TEM measurement. W.A.K. and J.E.M. contributed to the gate dielectric preparation. A.A. did the device simulation. C.A.R., E.Z., D.E.I. and Q.L. revised the manuscript. The project was designed by Q.L.

Ethics declarations

Competing interests

The authors declare no competing financial interests.

Rights and permissions

This work is licensed under a Creative Commons Attribution-NonCommercial-ShareAlike 3.0 Unported License. To view a copy of this license, visit http://creativecommons.org/licenses/by-nc-sa/3.0/

About this article

Cite this article

Zhu, H., Richter, C., Zhao, E. et al. Topological Insulator Bi2Se3 Nanowire High Performance Field-Effect Transistors. Sci Rep 3, 1757 (2013). https://doi.org/10.1038/srep01757

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/srep01757

This article is cited by

-

Preparation of large Cu3Sn single crystal by Czochralski method

Journal of the Korean Physical Society (2022)

-

Topological electronics

Communications Physics (2021)

-

Bi2Se3 Sensitized TiO2 Nanotube Films for Photogenerated Cathodic Protection of 304 Stainless Steel Under Visible Light

Nanoscale Research Letters (2018)

-

High performance broadband photodetector using fabricated nanowires of bismuth selenide

Scientific Reports (2016)

-

Ultrafast helicity control of surface currents in topological insulators with near-unity fidelity

Nature Communications (2015)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.

, the inset above shows a magnified region of the nanowire; (c) Schematic of a Bi2Se3 nanowire FET and (d) TEM image of the cross-section of a Bi2Se3 nanowire FET.

, the inset above shows a magnified region of the nanowire; (c) Schematic of a Bi2Se3 nanowire FET and (d) TEM image of the cross-section of a Bi2Se3 nanowire FET.