Development of a Digitally Controlled Inductive Power Transfer System with Post-Regulation for Variable Load Demand

Abstract

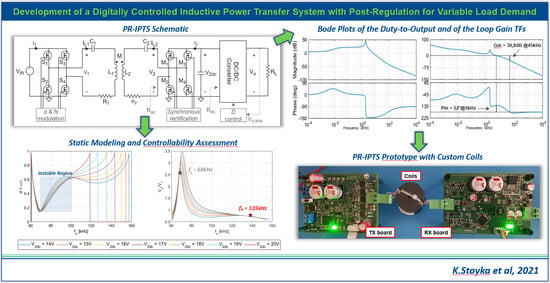

:1. Introduction

1.1. Overview of IPTS Architectures and Control Techniques

2. Static Modeling of Post-Regulated IPTS

2.1. Post-Regulated IPTS (PR-IPTS)

2.2. Static Modeling of PR-IPTS

2.3. Compensation Capacitors Selection

2.4. Static Modeling Results

2.5. PR-IPTS Controllability Assessment

3. Dynamic Modeling and Control of PR-IPTS

3.1. Dynamic Modeling of IPT Stage

3.2. Small-Signal Modeling of PR-IPTS

3.3. Digital Voltage Mode Control Design of Post-Regulator

4. Experimental Prototype

4.1. IPT Coil Realization

4.2. PR-IPTS Boards

4.3. Experimental Results

4.3.1. Efficiency Assessment with Electronic Load

4.3.2. Output Voltage Regulation under Variable Load Conditions

4.3.3. Battery Charging Test

4.4. Results Discussion

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Ruffo, R.; Cirimele, V.; Diana, M.; Khalilian, M.; La Ganga, A.; Guglielmi, P. Sensorless control of the charging process of a dynamic inductive power transfer system with an interleaved nine-phase boost converter. IEEE Trans. Ind. Electron. 2018, 65, 7630–7639. [Google Scholar] [CrossRef]

- Cirimele, V.; Diana, M.; Freschi, F.; Mitolo, M. Inductive power transfer for automotive applications state-of-the-art and future trends. IEEE Trans. Ind. Appl. 2018, 54, 4069–4079. [Google Scholar] [CrossRef]

- Yeo, T.-D.; Kwon, D.; Khang, S.-T.; Yu, J.-W. Design of Maximum Efficiency Tracking Control Scheme for Closed-Loop Wireless Power Charging System Employing Series Resonant Tank. IEEE Trans. Power Electron. 2017, 32, 471–478. [Google Scholar] [CrossRef]

- Al-Attar, A.; Attia, S.A.; Al-Bialy, A.; Abdelatif, E.N.; Al-Gazar, A.S.; Salem, A.; Badr, B.M. Wireless Power Transfer for Toys and Portable Devices. In Proceedings of the IEEE Conference on Power Electronics and Renewable Energy (CPERE), Aswan, Egypt, 23–25 October 2019; pp. 479–484. [Google Scholar] [CrossRef]

- Haerinia, M.; Shadid, R. Wireless Power Transfer Approaches for Medical Implants: A Review. Signals 2020, 1, 12. [Google Scholar] [CrossRef]

- Mao, Z.; Han, H.; Zhu, Q.; Su, M.; Peng, T. New concept of wireless power grid for industrial and home application. In Proceedings of the 2018 IEEE International Conference on Industrial Electronics for Sustainable Energy Systems (IESES), Hamilton, New Zealand, 31 January–2 February 2018. [Google Scholar] [CrossRef]

- Fadhil, H.A.; Abdulqader, S.G.; Aljunid, S.A. Implementation of wireless power transfer system for Smart Home applications. In Proceedings of the IEEE 8th GCC Conference & Exhibition, Muscat, Oman, 1–4 February 2015. [Google Scholar] [CrossRef]

- Mano, M.; Sankar, R. Wireless Charger Networking for Mobile Devices using Bluetooth Technologies. Int. J. Linguist. Comput. Appl. (IJLCA) 2018, 5, 1–3. [Google Scholar]

- Wang, C.-S.; Stielau, O.H.; Covic, G.A. Design Considerations for a Contactless Electric Vehicle Battery Charger. IEEE Trans. Ind. Electron. 2005, 52, 1308–1314. [Google Scholar] [CrossRef]

- Würth Elektronik, REDEXPERT. Available online: https://redexpert.we-online.com/redexpert/#/ (accessed on 1 September 2021).

- TDK, Wireless Power Transfer. Available online: https://product.tdk.com/en/products/wireless-charge/index.html (accessed on 26 August 2021).

- Abracon, Wireless Charging. Available online: https://abracon.com/parametric/wirelesscharging (accessed on 27 August 2021).

- Zahid, Z.U.; Dalala, Z.M.; Zheng, C.; Chen, R.; Faraci, W.E.; Lai, J.-S.; Lisi, G.; Anderson, D. Modeling and Control of Series–Series Compensated Inductive Power Transfer System. IEEE J. Emerg. Sel. Top. Power Electron. 2013, 3, 111–123. [Google Scholar] [CrossRef]

- Liu, F.; Lei, W.; Wang, T.; Nie, C.; Wang, Y. A phase-shift soft-switching control strategy for dual active wireless power transfer system. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, USA, 1–5 October 2017. [Google Scholar] [CrossRef]

- Ahn, D.; Kim, S.; Moon, J.; Cho, I.-K. Wireless Power Transfer with Automatic Feedback Control of Load Resistance Transformation. IEEE Trans. Power Electron. 2016, 31, 7876–7886. [Google Scholar] [CrossRef]

- Li, H.; Li, J.; Wang, K.; Chen, W.; Yang, X. A Maximum Efficiency Point Tracking Control Scheme for Wireless Power Transfer Systems Using Magnetic Resonant Coupling. IEEE Trans. Power Electron. 2015, 30, 3998–4008. [Google Scholar] [CrossRef]

- Chen, Q.; Jiang, L.; Hou, J.; Ren, X.; Ruan, X. Research on bidirectional contactless resonant converter for energy charging between EVs. In Proceedings of the 39th Annual Conference of the IEEE Industrial Electronics Society (IECON), Vienna, Austria, 10–13 November 2013. [Google Scholar] [CrossRef]

- Berger, A.; Agostinelli, M.; Vesti, S.; Oliver, J.A.; Cobos, J.A.; Huemer, M. A Wireless Charging System Applying Phase-Shift and Amplitude Control to Maximize Efficiency and Extractable Power. IEEE Trans. Power Electron. 2015, 30, 6338–6348. [Google Scholar] [CrossRef]

- Fu, M.; Yin, H.; Zhu, X.; Ma, C. Analysis and Tracking of Optimal Load in Wireless Power Transfer Systems. IEEE Trans. Power Electron. 2015, 30, 3952–3963. [Google Scholar] [CrossRef]

- Zhong, W.X.; Hui, S.Y.R. Maximum Energy Efficiency Tracking for Wireless Power Transfer Systems. IEEE Trans. Power Electron. 2015, 30, 4025–4034. [Google Scholar] [CrossRef] [Green Version]

- Yang, Y.; Zhong, W.; Kiratipongvoot, S.; Tan, S.-C.; Hui, S.Y.R. Dynamic Improvement of Series–Series Compensated Wireless Power Transfer Systems Using Discrete Sliding Mode Control. IEEE Trans. Power Electron. 2018, 33, 6351–6360. [Google Scholar] [CrossRef]

- Li, T.; Wang, X.; Zheng, S.; Liu, C. An Efficient Topology for Wireless Power Transfer over a Wide Range of Loading Conditions. Energies 2018, 11, 141. [Google Scholar] [CrossRef] [Green Version]

- Di Capua, G.; Femia, N. A Critical Investigation of Coupled Inductors SEPIC Design Issues. IEEE Trans. Ind. Electron. 2014, 61, 2724–2734. [Google Scholar] [CrossRef]

- Ishihara, H.; Moritsuka, F.; Kudo, H.; Obayashi, S.; Itakura, T.; Matsushita, A.; Mochikawa, H.; Otaka, S. A voltage ratio-based efficiency control method for 3 kW wireless power transmission. In Proceedings of the 2014 IEEE Applied Power Electronics Conference and Exposition (APEC), Fort Worth, TX, USA, 16–20 March 2014. [Google Scholar] [CrossRef]

- Tang, X.; Zeng, J.; Pun, K.P.; Mai, S.; Zhang, C.; Wang, Z. Low-Cost Maximum Efficiency Tracking Method for Wireless Power Transfer Systems. IEEE Trans. Power Electron. 2018, 33, 5317–5329. [Google Scholar] [CrossRef]

- Patil, D.; Sirico, M.; Gu, L.; Fahimi, B. Maximum efficiency tracking in wireless power transfer for battery charger: Phase shift and frequency control. In Proceedings of the 2016 IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, USA, 18–22 September 2016. [Google Scholar] [CrossRef]

- Li, H.; Wang, K.; Huang, L.; Chen, W.; Yang, X. Dynamic Modeling Based on Coupled Modes for Wireless Power Transfer Systems. IEEE Trans. Power Electron. 2015, 30, 6245–6253. [Google Scholar] [CrossRef]

- Li, H.; Tang, Y.; Wang, K.; Yang, X. Analysis and control of post regulation of wireless power transfer systems. In Proceedings of the 2016 IEEE 2nd Annual Southern Power Electronics Conference (SPEC), Auckland, New Zealand, 5–8 December 2016; pp. 1–5. [Google Scholar] [CrossRef]

- Infineon Technologies, SmartRectifier IR1161LPbF Datasheet. 2016. Available online: https://www.infineon.com/dgdl/ir1161lpbf.pdf?fileId=5546d462533600a4015355c439a5164d (accessed on 28 June 2021).

- Hurtuk, P.; Radvan, R.; Frivaldský, M. Full bridge converter with synchronous rectifiers for low output voltage application. In Proceedings of the 2011 International Conference on Applied Electronics, Pilsen, Czech Republic, 7–8 September 2011. [Google Scholar]

- Zhang, W.; Wong, S.; Tse, C.K.; Chen, Q. Design for Efficiency Optimization and Voltage Controllability of Series–Series Compensated Inductive Power Transfer Systems. IEEE Trans. Power Electron. 2014, 29, 191–200. [Google Scholar] [CrossRef]

- Venable, H.D. The K Factor: A New Mathematical Tool for Stability Analysis. In Proceedings of the 10th International Solid-State Power Electronics Conference (Powercon 10), San Diego, CA, USA, 22–24 March 1983. [Google Scholar]

- Biricha Digital Power Ltd., Digital PSU Plant Measurement 2017. Available online: https://www.biricha.com/uploads/8/9/8/0/89803127/digital_plant_measurement_reviewed.pdf (accessed on 21 June 2021).

- Peterchev, A.V.; Sanders, S.R. Quantization resolution and limit cycling in digitally controlled PWM converters. IEEE Trans. Power Electron. 2003, 18, 301–308. [Google Scholar] [CrossRef] [Green Version]

- Cho, J.; Sun, J.; Kim, H.; Fan, J.; Lu, Y.; Pan, S. Coil design for 100 KHz and 6.78 MHz WPT system: Litz and solid wires and winding methods. In Proceedings of the 2017 IEEE International Symposium on Electromagnetic Compatibility & Signal/Power Integrity (EMCSI), Washington, DC, USA, 7–11 August 2017. [Google Scholar] [CrossRef]

- Ferroxcube, P36/22 P Cores and Accessories. 2008. Available online: http://ferroxcube.home.pl/prod/assets/p3622.pdf (accessed on 5 July 2021).

- Extech Instruments LCR200 Passive Components LCR Meter. Available online: http://www.extech.com/products/LCR200 (accessed on 6 July 2021).

- Infineon Technologies, XMC1300 AB-Step Reference Manual, V1.3 2016-08. Available online: https://www.infineon.com/dgdl/Infineon-xmc1300-AB_rm-UM-v01_03-EN.pdf?fileId=5546d46249cd1014014a0a8436965e28 (accessed on 6 July 2021).

- Infineon Technologies, DAVE™—Professional Development Platform for XMC™ Microcontrollers. Available online: https://infineoncommunity.com/dave-download_id645 (accessed on 13 July 2021).

- Infineon Technologies, IRS2106/IRS21064(S)PbF Datasheet, No. PD60246. Available online: https://www.infineon.com/dgdl/Infineon-IRS2106-DataSheet-v01_00-EN.pdf?fileId=5546d462533600a4015356763aa527a3 (accessed on 15 July 2021).

- Infineon Technologies, XMC4100/XMC4200 Reference Manual, V1.6 2016-07. Available online: https://www.infineon.com/dgdl/Infineon-xmc4100_xmc4200_rm_v1.6_2016-UM-v01_06-EN.pdf?fileId=db3a30433afc7e3e013b3c44ccd35c20 (accessed on 16 July 2021).

- Infineon Technologies, IRS2011(S)PBF Datasheet. 2015. Available online: https://www.infineon.com/dgdl/Infineon-IRS2011-DataSheet-v01_00-EN.pdf?fileId=5546d462533600a401535675c19f2784 (accessed on 12 July 2021).

- Battery pack 12 V 10 Ah Rechargeable High Quality Lithium F2D5. Available online: https://www.aftertech.eu/pacco-batteria-12-volt-10000mah-10ah-12v-ricaricabile-alta-qualita-litio-f2d5-p-16292.html (accessed on 15 July 2021).

| Vin (V) | Vo (V) | RL (Ω) | L1 (µH) | R1 (mΩ) | L2 (µH) | R2 (mΩ) | M (µH) |

|---|---|---|---|---|---|---|---|

| 24 | 12 | 7 | 23 | 67 | 23 | 64 | 12.2 |

| V2dc (V) | Vo (V) | fBuck (kHz) | RL (Ω) | Lo (µH) | Co (µF) | ESRo (mΩ) | Cf (µF) |

|---|---|---|---|---|---|---|---|

| 14 | 12 | 100 | 7 | 22 | 440 | 5 | 2068 |

| ωz1 (rad/s) | ωp1 (rad/s) | ωp2 (rad/s) |

|---|---|---|

| 5.99 × 103 | 683.86 | 1.65 × 105 |

| a1 | a2 | a3 | |

| 1.193312123257 | −0.202654517506 | 0.009342394250 | |

| b0 | b1 | b2 | b3 |

| 0.824716092259 | −0.728775227352 | −0.821925844304 | 0.731565475307 |

| Gvd0 | HV | VFS (V) | Nbit | resADC (V) | NDPWM | tres (ps) | resDPWM | KP |

|---|---|---|---|---|---|---|---|---|

| 1.8474 | 0.1522 | 3.3 | 12 | 8.059 × 10−4 | 204,800 | 48.828 | 4.883 × 10−6 | 1084.1 |

| lg (mm) | L1, L2 (µH) | RL1, RL2 (mΩ) | k |

|---|---|---|---|

| 1.5 | 35 | 50 | 0.75 |

| 3 | 23 | 50 | 0.53 |

| 6 | 20 | 50 | 0.34 |

| Circuit Components | Values |

|---|---|

| Inverter MOSFETs S1–S4 | IPD50N04S4–10: Rds = 9.3 mΩ, Qg = 14 nC |

| Rectifier MOSFETs M1–M4 | BSZ070N08LS5: Rds = 7 mΩ, Qg = 14 nC |

| Buck half bridge | BSC0993ND: RdsHS = 4.2 mΩ, QgHS = 13 nC |

| MOSFETs MHS-MLS | RdsLS = 5.6 mΩ, QgLS = 6.7 nC |

| TX and RX coils L1, L2 | L1 = L2 = 23 µH, RL1 = RL2 = 50 mΩ |

| Buck output inductor Lo | Lo = 22 µH, RLo = 23 mΩ |

| TX and RX compensation capacitors C1, C2 | C1 = 200 nF, C2 = 100 nF |

| IPTS input capacitor Cin | Cin = 2440 µF |

| Intermediate bus capacitor Cf | Cf = 2068 µF |

| Buck output capacitor Co | Co = 440 µF, ESRo = 5 mΩ |

| RL (Ω) | Po (W) | fs (kHz) | V2dc (V) | ηmax |

|---|---|---|---|---|

| 5 | 28.8 | 120 | 15.0 | 0.917 |

| 7 | 20.6 | 115 | 14.1 | 0.903 |

| 14 | 10.3 | 105 | 14.0 | 0.792 |

| 24 | 6.0 | 140 | 14.0 | 0.721 |

| Reference | TX/RX Coil Size | Air Gap | Frequency | Power | Efficiency |

|---|---|---|---|---|---|

| This work | 36/36 mm | 3 mm | 100–160 kHz | 6–35 W | 72–92% |

| [13] | N/A | 70 mm | 165–180 kHz | 2.5–3.7 kW | N/A |

| [14] | N/A | N/A | 95.6 kHz | 9–90 W | 74–90% |

| [16] | 270/270 mm | 250 mm | 515 kHz | 25–100 W | 74–79% |

| [17] | 100 × 58/100 × 58 mm | 5 mm | 50 kHz | 300–1800W | 60–77% |

| [18] | 43/28 mm | 3 mm | 140 kHz | 1–11 W | 69–78% |

| [19] | 320/320 mm | 70 mm | 13.56 MHz | 40 W | 70% |

| [20] | 27/27 mm | N/A | 97.56 kHz | 4.5 W | 65% |

| [21] | 310/310 mm | N/A | 100 kHz | 5.6 W | 60% |

| [22] | 53 × 53/53 × 53 mm | 12 mm | 100 kHz | 1–10 W | 34–70% |

| [24] | 500 × 500/500 × 500 mm | 100 mm | 85 kHz | 3 kW | 95% |

| [25] | 43/43 mm | 23.5 mm | 592 kHz | 0.25–5 W | 73% |

| [26] | N/A | N/A | 92–110 kHz | 100–600 W | 65–78% |

| Reference | Rectification Type | Pre/Post-Regulation | TX–RX Communication | Output Voltage Regulation | Efficiency Maximization Control |

|---|---|---|---|---|---|

| This work | Synchronous | Post | No | Yes | No |

| [13] | Passive | No | Yes | Yes | No |

| [14] | Active | No | No | Yes | No |

| [16] | Passive | Pre and post | Yes | Yes | Yes |

| [17] | Active | No | No | Yes | No |

| [18] | Active | Post | Yes | No | No |

| [19] | Passive | Post | Yes | No | Yes |

| [20] | Passive | Post | No | Yes | Yes |

| [21] | Passive | Post | No | Yes | Yes |

| [22] | Passive | Post | No | Yes | Yes |

| [24] | Passive | Pre and post | Yes | No | Yes |

| [25] | Regulating | No | No | Yes | Yes |

| [26] | Passive | Post | No | Yes | Yes |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Stoyka, K.; Vitale, A.; Costarella, M.; Avella, A.; Pucciarelli, M.; Visconti, P. Development of a Digitally Controlled Inductive Power Transfer System with Post-Regulation for Variable Load Demand. Electronics 2022, 11, 58. https://doi.org/10.3390/electronics11010058

Stoyka K, Vitale A, Costarella M, Avella A, Pucciarelli M, Visconti P. Development of a Digitally Controlled Inductive Power Transfer System with Post-Regulation for Variable Load Demand. Electronics. 2022; 11(1):58. https://doi.org/10.3390/electronics11010058

Chicago/Turabian StyleStoyka, Kateryna, Antonio Vitale, Massimo Costarella, Alfonso Avella, Mario Pucciarelli, and Paolo Visconti. 2022. "Development of a Digitally Controlled Inductive Power Transfer System with Post-Regulation for Variable Load Demand" Electronics 11, no. 1: 58. https://doi.org/10.3390/electronics11010058